Overview

R

CF ![]()

![]() System ACE

System ACE

SysACE

INTC

OPB

Bus

PLB BRAM |

|

OPB2PLB |

|

Bridge | DDR |

PLB | |

Bus |

|

256MB

DDR DIMM

RS232

SMBus

SPI

GPIO / LEDs

GPIO SPI SMBus UART

PCI Bridge

PLB2OPB

Bridge

PPC

405

OCM

Bus

OCM BRAM

XC2VP30

FF896

8 RocketIO MGTs 3 LVDS pairs 1 LVDS Clock pair | 38 | |

|

|

|

| 39 LVDS Pairs | 1 Clock |

PM1

PM2

3.3V PCI

RJ45 |

|

|

| Intel GD82559 |

| TI |

|

|

| 10/100 Ethernet NIC |

| PCI 2250 | |

|

|

|

|

| ||

|

|

|

|

|

|

|

5V PCI

5V PCI

Slots

3.3V PCI

Slots

AMD |

|

|

|

|

|

|

|

|

|

|

| RS232 |

|

|

|

|

|

|

|

|

|

|

| ||

Flash |

|

|

|

|

|

|

|

|

|

|

| (2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GPIO |

|

|

|

| ALi |

|

|

|

| PS/2 | ||

|

|

|

|

|

|

|

| K/M | ||||

|

|

|

|

|

| |||||||

|

|

|

| M1535D+ |

|

|

| |||||

|

|

|

| |||||||||

IDE |

|

|

| Parallel | ||||||||

|

|

| South Bridge |

|

|

|

| |||||

(2) |

|

|

|

|

|

|

| Port | ||||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

USB |

|

|

|

|

|

|

|

|

|

|

| SMBus |

(2) |

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Audio |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

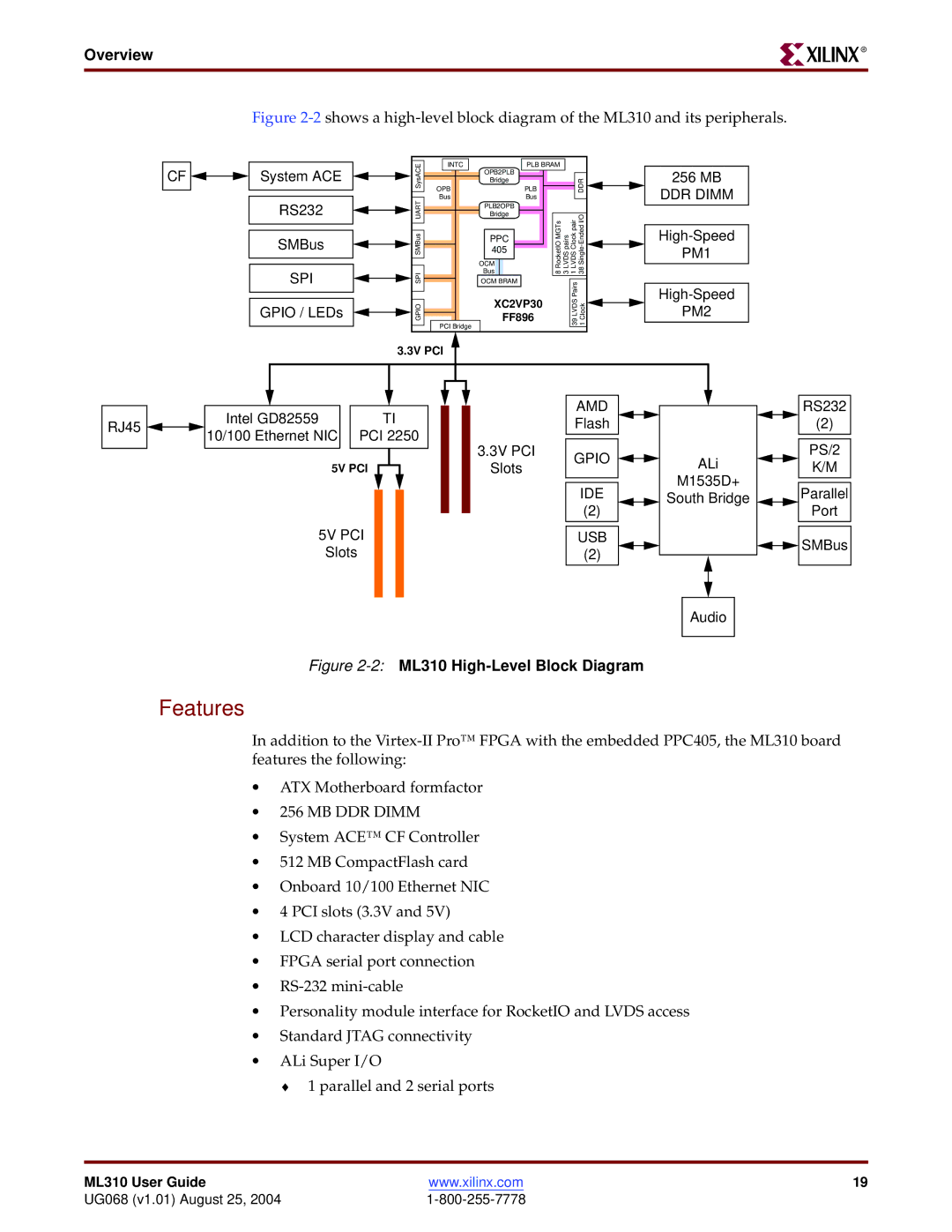

Figure 2-2: ML310 High-Level Block Diagram

Features

In addition to the

•ATX Motherboard formfactor

•256 MB DDR DIMM

•System ACE™ CF Controller

•512 MB CompactFlash card

•Onboard 10/100 Ethernet NIC

•4 PCI slots (3.3V and 5V)

•LCD character display and cable

•FPGA serial port connection

•

•Personality module interface for RocketIO and LVDS access

•Standard JTAG connectivity

•ALi Super I/O

♦ 1 parallel and 2 serial ports

ML310 User Guide | www.xilinx.com | 19 |

UG068 (v1.01) August 25, 2004 |

|