R

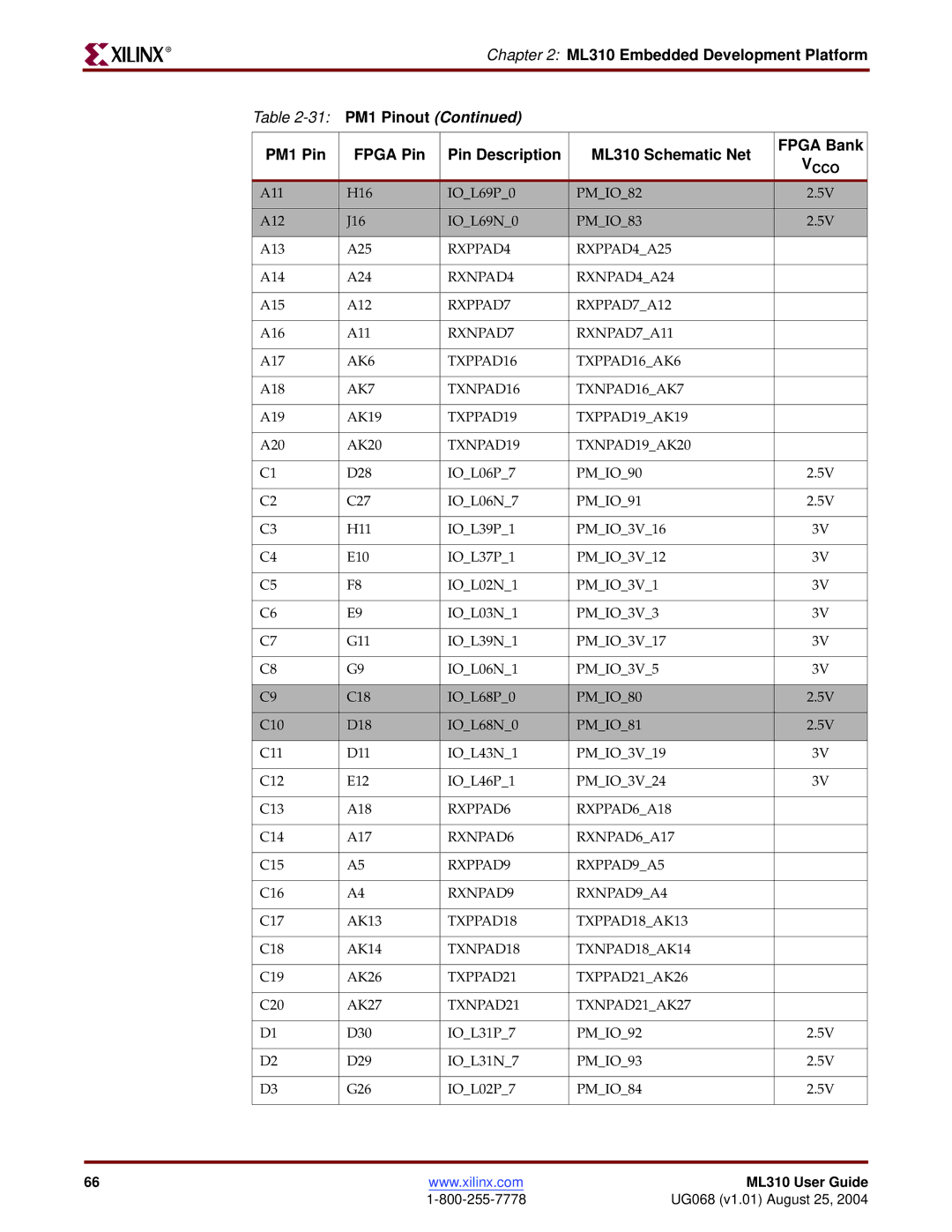

Chapter 2: ML310 Embedded Development Platform

Table | PM1 Pinout (Continued) |

|

| ||

|

|

|

|

| |

PM1 Pin | FPGA Pin | Pin Description | ML310 Schematic Net | FPGA Bank | |

VCCO | |||||

|

|

|

| ||

A11 | H16 | IO_L69P_0 | PM_IO_82 | 2.5V | |

|

|

|

|

| |

A12 | J16 | IO_L69N_0 | PM_IO_83 | 2.5V | |

|

|

|

|

| |

A13 | A25 | RXPPAD4 | RXPPAD4_A25 |

| |

|

|

|

|

| |

A14 | A24 | RXNPAD4 | RXNPAD4_A24 |

| |

|

|

|

|

| |

A15 | A12 | RXPPAD7 | RXPPAD7_A12 |

| |

|

|

|

|

| |

A16 | A11 | RXNPAD7 | RXNPAD7_A11 |

| |

|

|

|

|

| |

A17 | AK6 | TXPPAD16 | TXPPAD16_AK6 |

| |

|

|

|

|

| |

A18 | AK7 | TXNPAD16 | TXNPAD16_AK7 |

| |

|

|

|

|

| |

A19 | AK19 | TXPPAD19 | TXPPAD19_AK19 |

| |

|

|

|

|

| |

A20 | AK20 | TXNPAD19 | TXNPAD19_AK20 |

| |

|

|

|

|

| |

C1 | D28 | IO_L06P_7 | PM_IO_90 | 2.5V | |

|

|

|

|

| |

C2 | C27 | IO_L06N_7 | PM_IO_91 | 2.5V | |

|

|

|

|

| |

C3 | H11 | IO_L39P_1 | PM_IO_3V_16 | 3V | |

|

|

|

|

| |

C4 | E10 | IO_L37P_1 | PM_IO_3V_12 | 3V | |

|

|

|

|

| |

C5 | F8 | IO_L02N_1 | PM_IO_3V_1 | 3V | |

|

|

|

|

| |

C6 | E9 | IO_L03N_1 | PM_IO_3V_3 | 3V | |

|

|

|

|

| |

C7 | G11 | IO_L39N_1 | PM_IO_3V_17 | 3V | |

|

|

|

|

| |

C8 | G9 | IO_L06N_1 | PM_IO_3V_5 | 3V | |

|

|

|

|

| |

C9 | C18 | IO_L68P_0 | PM_IO_80 | 2.5V | |

|

|

|

|

| |

C10 | D18 | IO_L68N_0 | PM_IO_81 | 2.5V | |

|

|

|

|

| |

C11 | D11 | IO_L43N_1 | PM_IO_3V_19 | 3V | |

|

|

|

|

| |

C12 | E12 | IO_L46P_1 | PM_IO_3V_24 | 3V | |

|

|

|

|

| |

C13 | A18 | RXPPAD6 | RXPPAD6_A18 |

| |

|

|

|

|

| |

C14 | A17 | RXNPAD6 | RXNPAD6_A17 |

| |

|

|

|

|

| |

C15 | A5 | RXPPAD9 | RXPPAD9_A5 |

| |

|

|

|

|

| |

C16 | A4 | RXNPAD9 | RXNPAD9_A4 |

| |

|

|

|

|

| |

C17 | AK13 | TXPPAD18 | TXPPAD18_AK13 |

| |

|

|

|

|

| |

C18 | AK14 | TXNPAD18 | TXNPAD18_AK14 |

| |

|

|

|

|

| |

C19 | AK26 | TXPPAD21 | TXPPAD21_AK26 |

| |

|

|

|

|

| |

C20 | AK27 | TXNPAD21 | TXNPAD21_AK27 |

| |

|

|

|

|

| |

D1 | D30 | IO_L31P_7 | PM_IO_92 | 2.5V | |

|

|

|

|

| |

D2 | D29 | IO_L31N_7 | PM_IO_93 | 2.5V | |

|

|

|

|

| |

D3 | G26 | IO_L02P_7 | PM_IO_84 | 2.5V | |

|

|

|

|

| |

66 | www.xilinx.com | ML310 User Guide |

| UG068 (v1.01) August 25, 2004 |