Board Hardware

Table

R

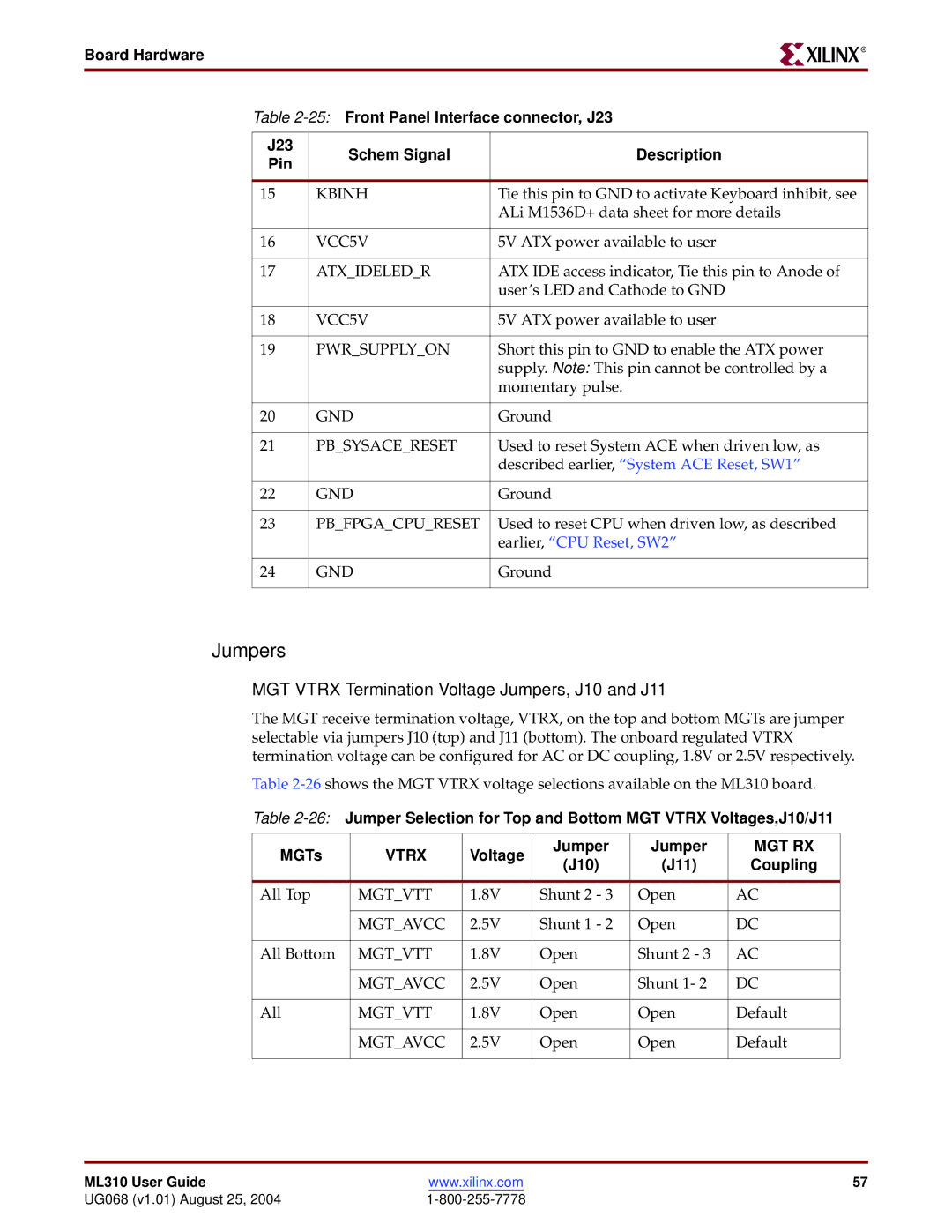

J23 | Schem Signal | Description | |

Pin | |||

|

| ||

|

|

| |

15 | KBINH | Tie this pin to GND to activate Keyboard inhibit, see | |

|

| ALi M1536D+ data sheet for more details | |

|

|

| |

16 | VCC5V | 5V ATX power available to user | |

|

|

| |

17 | ATX_IDELED_R | ATX IDE access indicator, Tie this pin to Anode of | |

|

| user’s LED and Cathode to GND | |

|

|

| |

18 | VCC5V | 5V ATX power available to user | |

|

|

| |

19 | PWR_SUPPLY_ON | Short this pin to GND to enable the ATX power | |

|

| supply. Note: This pin cannot be controlled by a | |

|

| momentary pulse. | |

|

|

| |

20 | GND | Ground | |

|

|

| |

21 | PB_SYSACE_RESET | Used to reset System ACE when driven low, as | |

|

| described earlier, “System ACE Reset, SW1” | |

|

|

| |

22 | GND | Ground | |

|

|

| |

23 | PB_FPGA_CPU_RESET | Used to reset CPU when driven low, as described | |

|

| earlier, “CPU Reset, SW2” | |

|

|

| |

24 | GND | Ground | |

|

|

|

Jumpers

MGT VTRX Termination Voltage Jumpers, J10 and J11

The MGT receive termination voltage, VTRX, on the top and bottom MGTs are jumper selectable via jumpers J10 (top) and J11 (bottom). The onboard regulated VTRX termination voltage can be configured for AC or DC coupling, 1.8V or 2.5V respectively.

Table

Table

MGTs | VTRX | Voltage | Jumper | Jumper | MGT RX | |

(J10) | (J11) | Coupling | ||||

|

|

| ||||

|

|

|

|

|

| |

All Top | MGT_VTT | 1.8V | Shunt 2 - 3 | Open | AC | |

|

|

|

|

|

| |

| MGT_AVCC | 2.5V | Shunt 1 - 2 | Open | DC | |

|

|

|

|

|

| |

All Bottom | MGT_VTT | 1.8V | Open | Shunt 2 - 3 | AC | |

|

|

|

|

|

| |

| MGT_AVCC | 2.5V | Open | Shunt 1- 2 | DC | |

|

|

|

|

|

| |

All | MGT_VTT | 1.8V | Open | Open | Default | |

|

|

|

|

|

| |

| MGT_AVCC | 2.5V | Open | Open | Default | |

|

|

|

|

|

|

ML310 User Guide | www.xilinx.com | 57 |

UG068 (v1.01) August 25, 2004 |

|