Design Guide

Intel 440GX AGPset

Intel440GX AGPset Design Guide

Contents

System Bus Clock Layout 6.3

Dimm Solution With FET Switches

6.4

6.5

ISA and X-Bus Signals

PIIX4E Power And Ground Pins

Thermals / Cooling Solutions 20.1

82371EB PIIX4E

FET Switches4 DIMM/FET Design

IntelPentiumII Processor LAI Issue

Voltage Regulator Control Silicon

Intel440GX AGPset Platform Reference Design

Example NLX Placement for a UP Intel Pentium II processor

Example ATX Placement for a UP Pentium II processor

Solution Space for Single Processor Design Based on Results

Solution Space for Single Processor Designs With Single-End

Intel Pentium II Processor and Intel 440GX AGPset

Tables

Intel Pentium II Processor and Intel 440GX AGPset 100 MHz

Motherboard Model MAB12,11,90#, MAB14,13,10, 4 DIMMs

Date Revision Description

Revision History

Intel440GX AGPset Design Guide

Introduction

Page

About This Design Guide

Introduction

References

Intel Pentium II Processor

Intel Pentium II Processor / Intel 440GX AGPset Overview

VCR

Intel 440GX AGPset

System Bus Interface

Dram Interface

Accelerated Graphics Port Interface

PCI-to-ISA/IDE Xcelerator PIIX4E

Wired for Management Initiative

PCI Interface

System Clocking

Instrumentation

Remote Service Boot

Design Recommendations

Power Management

Voltage Definitions

Remote Wake-Up

General Design Recommendations

Introduction

Motherboard Design

Page

BGA Quadrant Assignment

Major Signal Sections 82443GX Top View

ATX Form Factor

NLX Form Factor

Board Description

Four Layer Board Stack-up

Routing Guidelines

2 GTL+ Layout Recommendations

1 GTL+ Description

Single Processor Design

Single Processor Network Topology and Conditions

Single Processor Recommended Trace Lengths

Recommended Trace Lengths for Single Processor Design

Trace Minimum Length Maximum Length

Single Processor Systems-Single-End Termination SET

Dual Processor Systems

Dual Processor Network Topology and Conditions

Dual Processor Recommended Trace Lengths

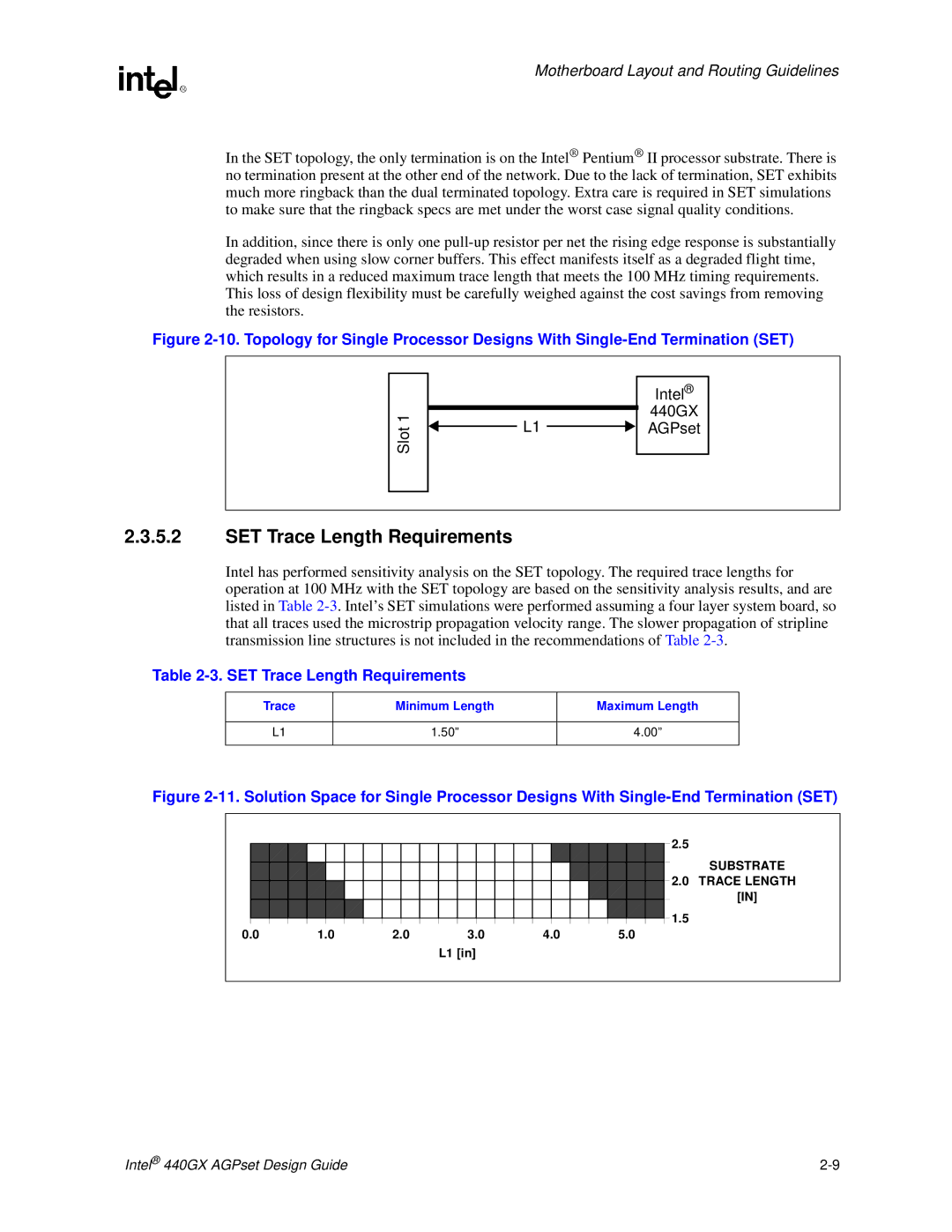

SET Trace Length Requirements

SET Trace Length Requirements

Additional Guidelines

Minimizing Crosstalk

Practical Considerations

Design Methodology

12. GTL+ Design Process

Performance Requirements

Pre-Layout Simulation Sensitivity Analysis

Topology Definition

Simulation Methodology

Recommended 100 MHz System Flight Time Specs

Post-Layout Simulation

Placement & Layout

Crosstalk and the Multi-Bit Adjustment Factor

Validation

Flight Time Measurement

Edge Guideline @ Processor Edge Spec @ Processor Core

Signal Quality Measurement

Term Description

Timing Analysis

11. Recommended 100 MHz System Flight Time Specs

10. Recommended 100 MHz System Timing Parameters

Timing Term Intel Pentium II Processor Intel 440GX AGPset

Timing Term Value

Connector

AGP Connector Up Option Layout Guidelines

AGP Layout and Routing Guidelines

12. Data and Associated Strobe

On-board AGP Compliant Device Down Option Layout Guidelines

14. Control Signal Line Length Recommendations

13. Source Synchronous Motherboard Recommendations

WidthSpace Trace Line Length Line Length Matching

16. Control Signal Line Length Recommendations

Compliant 82443GX Graphics Data Routing Device

15. Source Synchronous Motherboard Recommendations

82443GX Memory Subsystem Layout and Routing Guidelines

1 100 MHz 82443GX Memory Array Considerations

To 82443GX MDs & MECCs To DIMM10 DQs To DIMM32 DQs

Adding Additional Decoupling Capacitor

Matching the Reference Planes

Register

Register Data Control Clock

Trace Width vs. Trace Spacing

Memory Layout & Routing Guidelines

Switch 16212 Dimm Module

18. FET Switch DQ Route Example

82443GX Dimm Module

82443GX 0.6 0.4 0.6 0.4 Dimm Module

24. Motherboard Model-DQMB1,5, 4 DIMMs

19. Motherboard Model SRASB#, 4 DIMMs

20. Motherboard Model SCASA#, 4 DIMMs

21. Motherboard Model SCASB#, 4 DIMMs

22. Motherboard Model WEA#, 4 DIMMs

23. Motherboard Model WEB#, 4 DIMMs

24. Motherboard Model MAA140, 4 DIMMs

PCI Bus Routing Guidelines

3 4 Dimm Routing Guidelines no FET

25. Motherboard Model MAB12,11,90#, MAB14,13,10, 4 DIMMs

VCC3

Host Bridge Controller 492 BGA

Decoupling Guidelines Intel 440GX AGPset Platform

Clock Routing Spacing

Intel 440GX AGPset Clock Layout Recommendations

System Bus Clock Layout

014 018 Clock

Sdram Clock Layout

PCI Clock Layout

Net Trace Length Min Max Cap

440GX Ckbf Dlko

Net Trace Length Min Max Card Trace

AGP Clock Layout

Design Checklist

Page

Pull-up and Pull-down Resistor Values

Overview

Intel Pentium II Processor Checklist

Slot Connectivity Sheet 1

Processor Pin Pin Connection

Slot Connectivity Sheet 2

GND & Power Pin Definition

Slot Connectivity Sheet 3

Vtt VCC3 Reserved NC Vcc

Intel Pentium II Processor Clocks

Intel Pentium II Processor Signals

Design Checklist

Dual-Processor DP Slot 1 Checklist

Uni-Processor UP Slot 1 Checklist

Slot 1 Decoupling Capacitors

Voltage Regulator Module, VRM

1 CK100 100 MHz Clock Synthesizer

Intel 440GX AGPset Clocks

Processor Frequency Select

SEL100/66#

Gcke and Dclkwr Connection

Ckbf Sdram 1 to 18 Clock Buffer

82443GX Host Bridge

1 82443GX Interface

GX Connectivity Sheet 1

GX Connectivity Sheet 2

3 82443GX PCI Interface

2 82443GX GTL+ Bus Interface

GX Connectivity Sheet 3

VTTA, Vttb

Signal Description Register Pulled to ‘0’ Pulled to ‘1’

4 82443GX AGP Interface

Strapping Options

Intel 440GX AGPset Memory Interface

82443GX Pins/Connection Dimm Pins Pin Function

Sdram Connections

Sdram Connectivity

Registered Sdram

Dimm Solution With FET Switches

82371EB PIIX4E

Signal Names Connection

PIIX4E Connections

PIIX4E Connectivity Sheet 1

PIIX4E Connectivity Sheet 2

PIIX4E Connectivity Sheet 3

PIIX4E Connectivity Sheet 4

IDE Routing Guidelines

Signal Resistor

Cabling

Motherboard

PDD150 PDA20

Reset#

Pin32,34

IDE

PCI Bus Signals

PIIX4E Power And Ground Pins

PIIX4E PWR & GND

ISA and X-Bus Signals

ISA Signals

10. Non-PIIX4E PCI Signals

11. Non-PIIX4E ISA Signals

USB Interface

IDE Interface

12. Non-PIIX4E IDE

Dual-Footprint Flash Design

Flash Design

Flash Design Considerations

PLCC32 to TSOP40 PLCC32 to PSOP44 PDIP32 to TDIP40

XD70

Write Protection

13. Flash Vpp Recommendations

Power Management Signals

System and Test Signals

VCC3

Power Button Implementation

Miscellaneous

17 82093AA Ioapic

18.1 Max1617 Temperature Sensor

Manageability Devices

18.2 LM79 Microprocessor System Hardware Monitor

18.3 82558B LOM Checklist

Pin Number Pin Name Resistor Value Comment

Required in both a and B stepping designs

Software/BIOS

USB and Multi-processor Bios

Wake On LAN WOL Header

Thermals / Cooling Solutions

Mechanicals

Design Considerations

Electricals

Applications and Add-in Hardware

Layout Checklist

Routing and Board Fabrication

Design Consideration

Debug Recommendations

Page

Debug/Simulation Tools

Slot 1 Test Tools

Logic Analyzer Interface LAI

In-Target Probe ITP

Intel Pentium II Processor LAI Issue

Debug Features

Bus Functional Model BFM

4 I/O Buffer Models

Kohm

150 330 ohm

430 ohm

150 ohm

Debug Logic Recommendations

A20M# 150 330 ohm

PICD0# 150 ohm PICD1#

Debug Layout

Debug Procedures

Debug Considerations

Design Considerations

Debug Recommendations

Third Party Vendors

Page

Processors

Slot 1 Connector

GTL+ Bus Slot 1 Terminator Cards

Supplier Contact Phone

Voltage Regulator Control Silicon

Voltage Regulator Modules

Voltage Regulator Modules

Voltage Regulator Control Silicon Vendors

FET Switches4 DIMM/FET Design

Power Management Components

Intel 440GX AGPset

Clock Drivers

Other Processor Components

Reference Design Schematics

Page

Intel 440GX AGPset Platform Reference Design

82443GX Component System bus and Dram Interfaces

VRM

Power Connectors Front Panel Jumpers