www.ti.com

Peripheral Architecture

2.10 Interrupt Support

2.10.1Interrupt Events and Requests

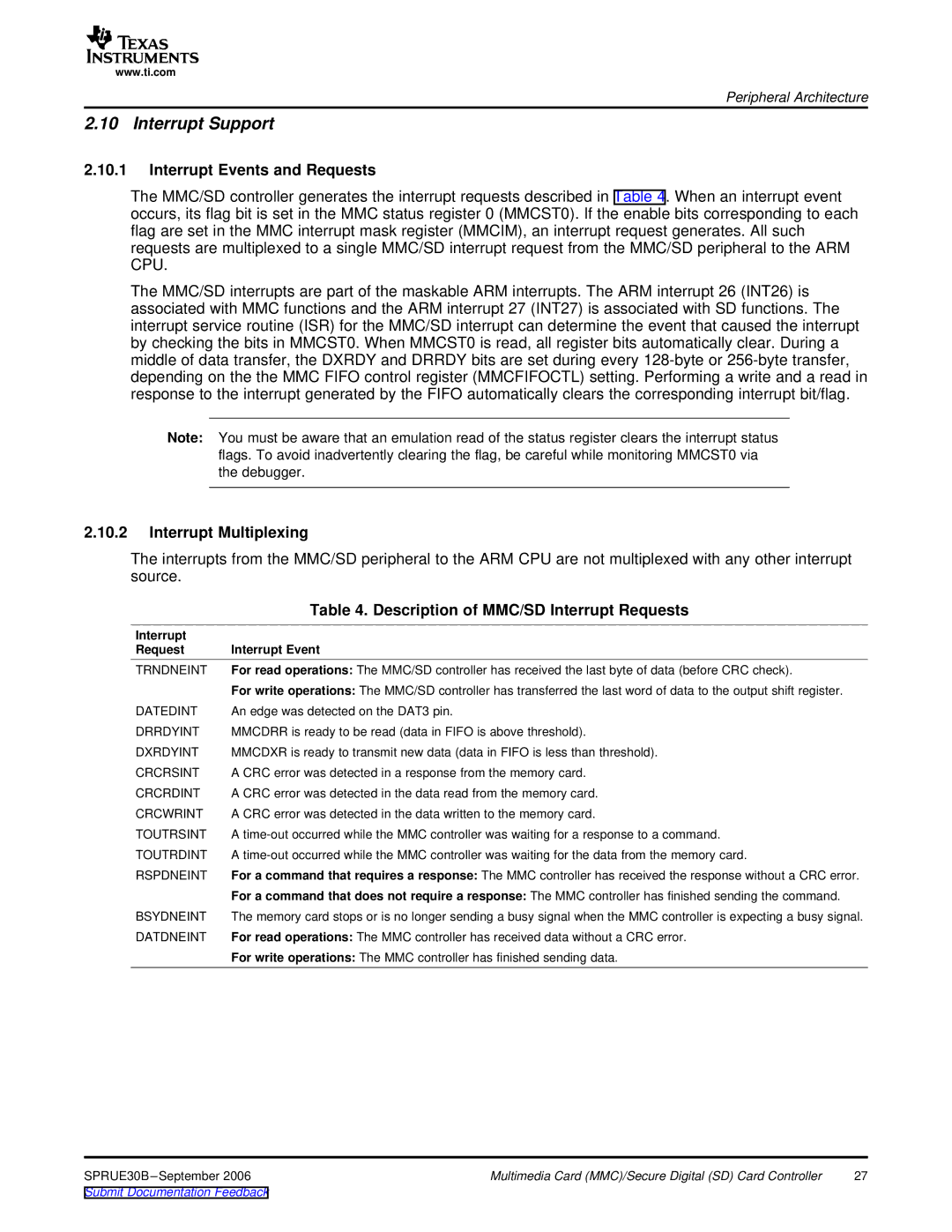

The MMC/SD controller generates the interrupt requests described in Table 4. When an interrupt event occurs, its flag bit is set in the MMC status register 0 (MMCST0). If the enable bits corresponding to each flag are set in the MMC interrupt mask register (MMCIM), an interrupt request generates. All such requests are multiplexed to a single MMC/SD interrupt request from the MMC/SD peripheral to the ARM CPU.

The MMC/SD interrupts are part of the maskable ARM interrupts. The ARM interrupt 26 (INT26) is associated with MMC functions and the ARM interrupt 27 (INT27) is associated with SD functions. The interrupt service routine (ISR) for the MMC/SD interrupt can determine the event that caused the interrupt by checking the bits in MMCST0. When MMCST0 is read, all register bits automatically clear. During a middle of data transfer, the DXRDY and DRRDY bits are set during every

Note: You must be aware that an emulation read of the status register clears the interrupt status flags. To avoid inadvertently clearing the flag, be careful while monitoring MMCST0 via the debugger.

2.10.2Interrupt Multiplexing

The interrupts from the MMC/SD peripheral to the ARM CPU are not multiplexed with any other interrupt source.

| Table 4. Description of MMC/SD Interrupt Requests |

Interrupt |

|

Request | Interrupt Event |

TRNDNEINT | For read operations: The MMC/SD controller has received the last byte of data (before CRC check). |

| For write operations: The MMC/SD controller has transferred the last word of data to the output shift register. |

DATEDINT | An edge was detected on the DAT3 pin. |

DRRDYINT | MMCDRR is ready to be read (data in FIFO is above threshold). |

DXRDYINT | MMCDXR is ready to transmit new data (data in FIFO is less than threshold). |

CRCRSINT | A CRC error was detected in a response from the memory card. |

CRCRDINT | A CRC error was detected in the data read from the memory card. |

CRCWRINT | A CRC error was detected in the data written to the memory card. |

TOUTRSINT | A |

TOUTRDINT | A |

RSPDNEINT | For a command that requires a response: The MMC controller has received the response without a CRC error. |

| For a command that does not require a response: The MMC controller has finished sending the command. |

BSYDNEINT | The memory card stops or is no longer sending a busy signal when the MMC controller is expecting a busy signal. |

DATDNEINT | For read operations: The MMC controller has received data without a CRC error. |

| For write operations: The MMC controller has finished sending data. |

SPRUE30B | Multimedia Card (MMC)/Secure Digital (SD) Card Controller | 27 |

Submit Documentation Feedback |

|

|