www.ti.com

Registers

4.5MMC Interrupt Mask Register (MMCIM)

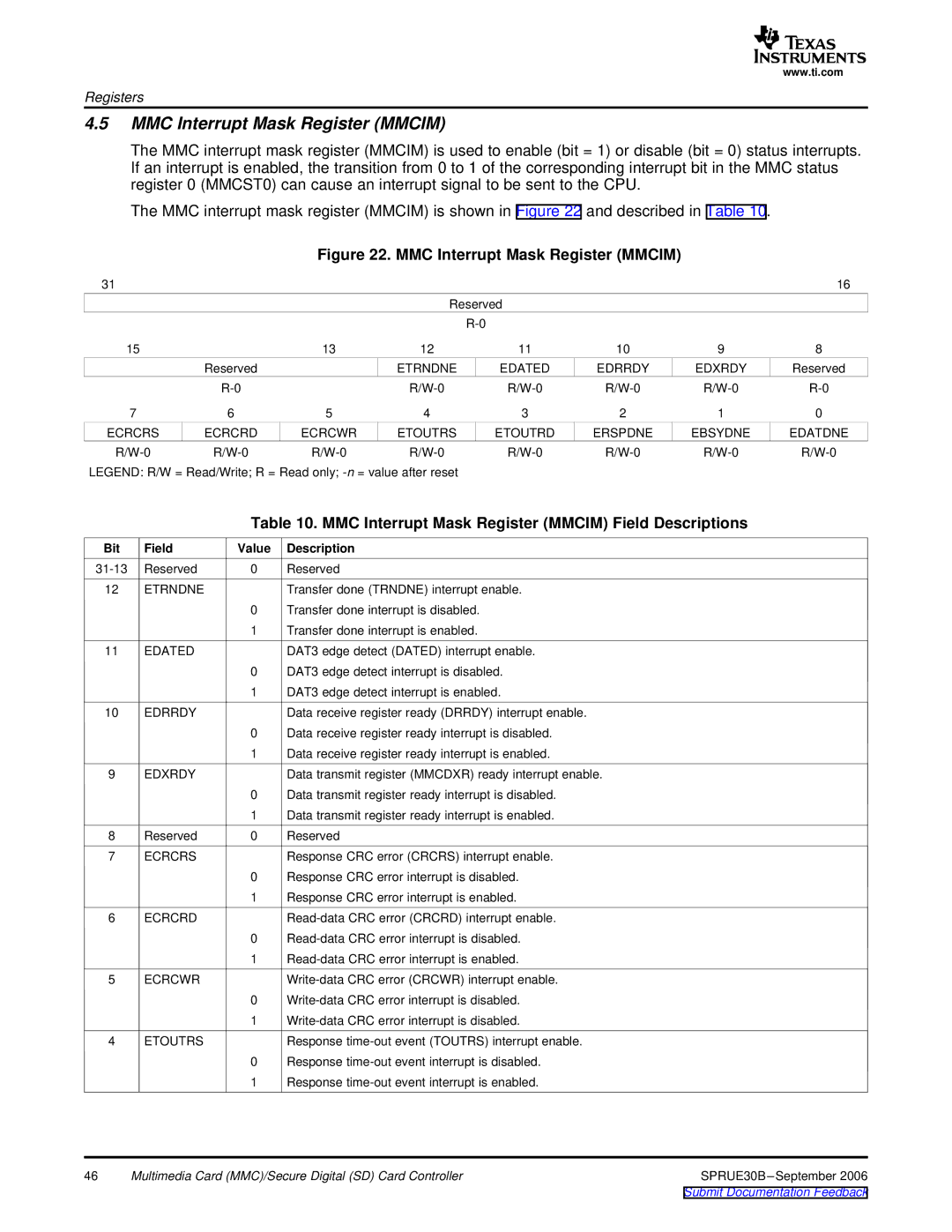

The MMC interrupt mask register (MMCIM) is used to enable (bit = 1) or disable (bit = 0) status interrupts. If an interrupt is enabled, the transition from 0 to 1 of the corresponding interrupt bit in the MMC status register 0 (MMCST0) can cause an interrupt signal to be sent to the CPU.

The MMC interrupt mask register (MMCIM) is shown in Figure 22 and described in Table 10.

Figure 22. MMC Interrupt Mask Register (MMCIM)

31 |

|

|

|

|

|

| 16 |

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

| |

15 |

| 13 | 12 | 11 | 10 | 9 | 8 |

| Reserved |

| ETRNDNE | EDATED | EDRRDY | EDXRDY | Reserved |

|

| ||||||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

ECRCRS | ECRCRD | ECRCWR | ETOUTRS | ETOUTRD | ERSPDNE | EBSYDNE | EDATDNE |

LEGEND: R/W = Read/Write; R = Read only;

Table 10. MMC Interrupt Mask Register (MMCIM) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

12 | ETRNDNE |

| Transfer done (TRNDNE) interrupt enable. |

|

| 0 | Transfer done interrupt is disabled. |

|

| 1 | Transfer done interrupt is enabled. |

11 | EDATED |

| DAT3 edge detect (DATED) interrupt enable. |

|

| 0 | DAT3 edge detect interrupt is disabled. |

|

| 1 | DAT3 edge detect interrupt is enabled. |

10 | EDRRDY |

| Data receive register ready (DRRDY) interrupt enable. |

|

| 0 | Data receive register ready interrupt is disabled. |

|

| 1 | Data receive register ready interrupt is enabled. |

9 | EDXRDY |

| Data transmit register (MMCDXR) ready interrupt enable. |

|

| 0 | Data transmit register ready interrupt is disabled. |

|

| 1 | Data transmit register ready interrupt is enabled. |

8 | Reserved | 0 | Reserved |

7 | ECRCRS |

| Response CRC error (CRCRS) interrupt enable. |

|

| 0 | Response CRC error interrupt is disabled. |

|

| 1 | Response CRC error interrupt is enabled. |

6 | ECRCRD |

| |

|

| 0 | |

|

| 1 | |

5 | ECRCWR |

| |

|

| 0 | |

|

| 1 | |

4 | ETOUTRS |

| Response |

|

| 0 | Response |

|

| 1 | Response |

46 | Multimedia Card (MMC)/Secure Digital (SD) Card Controller | SPRUE30B |

|

| Submit Documentation Feedback |