www.ti.com

Registers

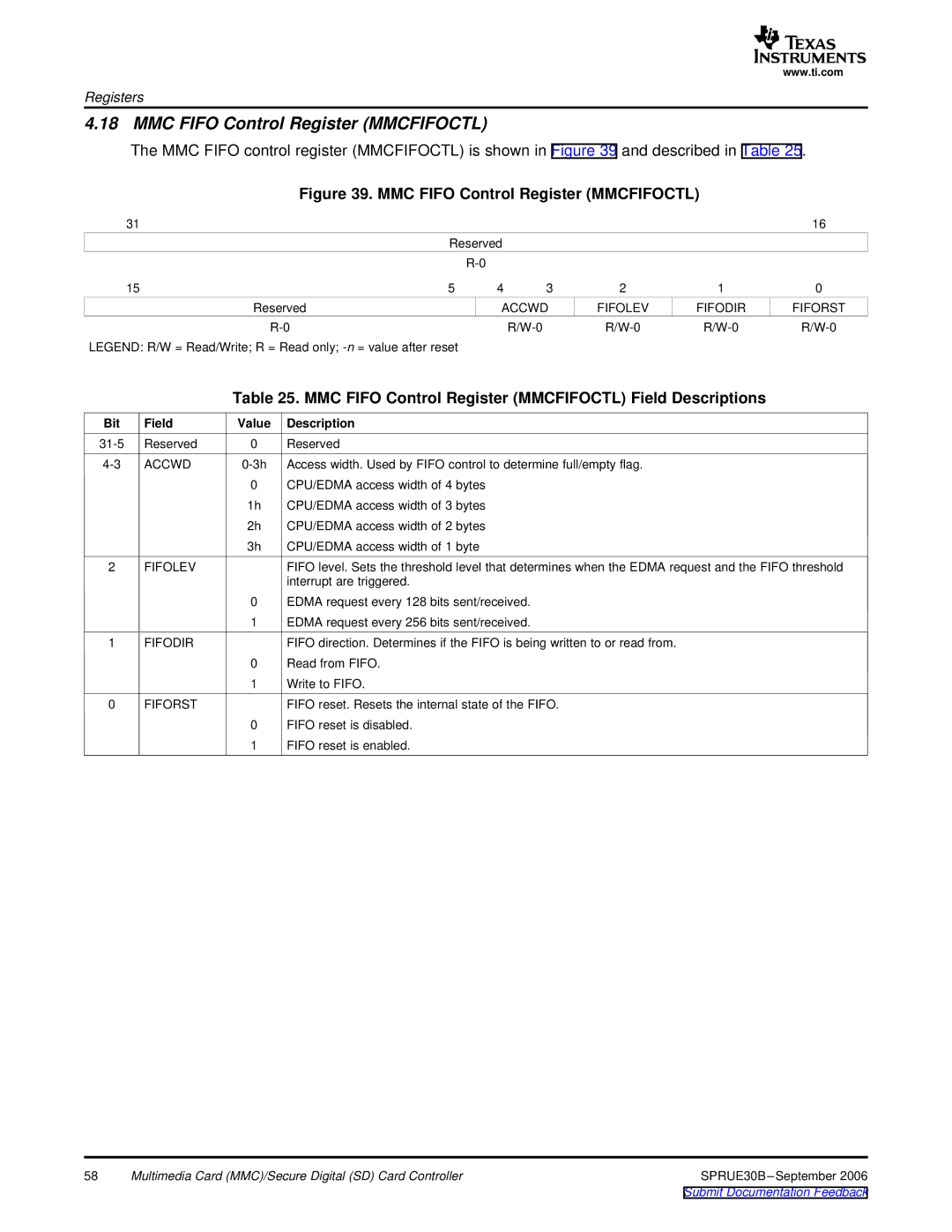

4.18 MMC FIFO Control Register (MMCFIFOCTL)

The MMC FIFO control register (MMCFIFOCTL) is shown in Figure 39 and described in Table 25.

Figure 39. MMC FIFO Control Register (MMCFIFOCTL)

31 |

|

|

|

|

| 16 |

| Reserved |

|

|

|

| |

|

|

|

|

|

| |

15 | 5 | 4 | 3 | 2 | 1 | 0 |

Reserved |

| ACCWD | FIFOLEV | FIFODIR | FIFORST | |

|

| |||||

LEGEND: R/W = Read/Write; R = Read only;

Table 25. MMC FIFO Control Register (MMCFIFOCTL) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

ACCWD | Access width. Used by FIFO control to determine full/empty flag. | ||

|

| 0 | CPU/EDMA access width of 4 bytes |

|

| 1h | CPU/EDMA access width of 3 bytes |

|

| 2h | CPU/EDMA access width of 2 bytes |

|

| 3h | CPU/EDMA access width of 1 byte |

2 | FIFOLEV |

| FIFO level. Sets the threshold level that determines when the EDMA request and the FIFO threshold |

|

|

| interrupt are triggered. |

|

| 0 | EDMA request every 128 bits sent/received. |

|

| 1 | EDMA request every 256 bits sent/received. |

1 | FIFODIR |

| FIFO direction. Determines if the FIFO is being written to or read from. |

|

| 0 | Read from FIFO. |

|

| 1 | Write to FIFO. |

0 | FIFORST |

| FIFO reset. Resets the internal state of the FIFO. |

|

| 0 | FIFO reset is disabled. |

|

| 1 | FIFO reset is enabled. |

58 | Multimedia Card (MMC)/Secure Digital (SD) Card Controller | SPRUE30B |

|

| Submit Documentation Feedback |