www.ti.com

Registers

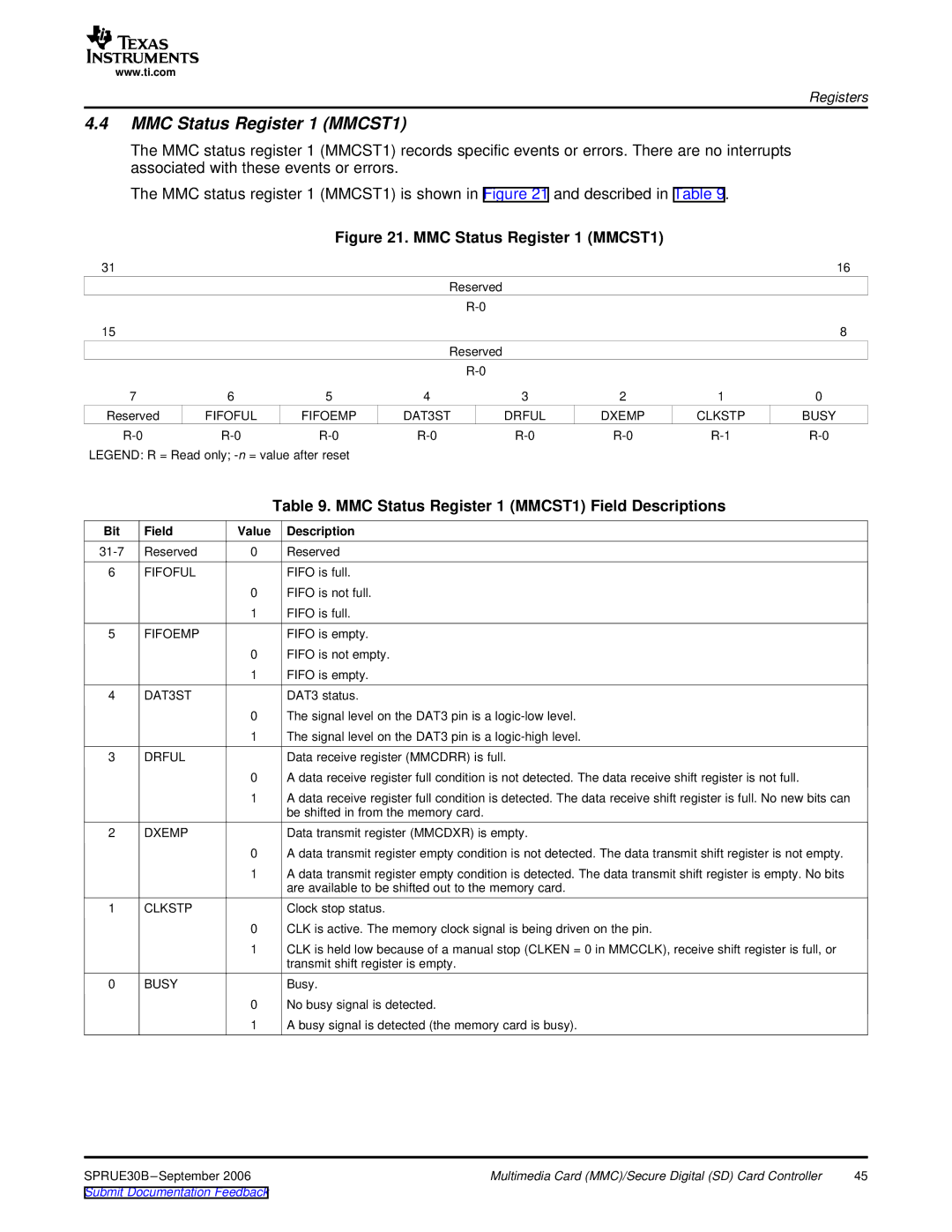

4.4MMC Status Register 1 (MMCST1)

The MMC status register 1 (MMCST1) records specific events or errors. There are no interrupts associated with these events or errors.

The MMC status register 1 (MMCST1) is shown in Figure 21 and described in Table 9.

|

| Figure 21. MMC Status Register 1 (MMCST1) |

|

| |||

31 |

|

|

|

|

|

| 16 |

|

|

| Reserved |

|

|

|

|

|

|

|

|

|

|

| |

15 |

|

|

|

|

|

| 8 |

|

|

| Reserved |

|

|

|

|

|

|

|

|

|

|

| |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Reserved | FIFOFUL | FIFOEMP | DAT3ST | DRFUL | DXEMP | CLKSTP | BUSY |

LEGEND: R = Read only; |

|

|

|

|

| ||

|

|

| Table 9. MMC Status Register 1 (MMCST1) Field Descriptions |

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

6 | FIFOFUL |

| FIFO is full. |

|

| 0 | FIFO is not full. |

|

| 1 | FIFO is full. |

5 | FIFOEMP |

| FIFO is empty. |

|

| 0 | FIFO is not empty. |

|

| 1 | FIFO is empty. |

4 | DAT3ST |

| DAT3 status. |

|

| 0 | The signal level on the DAT3 pin is a |

|

| 1 | The signal level on the DAT3 pin is a |

3 | DRFUL |

| Data receive register (MMCDRR) is full. |

|

| 0 | A data receive register full condition is not detected. The data receive shift register is not full. |

1A data receive register full condition is detected. The data receive shift register is full. No new bits can be shifted in from the memory card.

2 | DXEMP | Data transmit register (MMCDXR) is empty. |

| 0 | A data transmit register empty condition is not detected. The data transmit shift register is not empty. |

1A data transmit register empty condition is detected. The data transmit shift register is empty. No bits are available to be shifted out to the memory card.

1 | CLKSTP | Clock stop status. |

| 0 | CLK is active. The memory clock signal is being driven on the pin. |

| 1 | CLK is held low because of a manual stop (CLKEN = 0 in MMCCLK), receive shift register is full, or |

|

| transmit shift register is empty. |

0 | BUSY | Busy. |

| 0 | No busy signal is detected. |

| 1 | A busy signal is detected (the memory card is busy). |

SPRUE30B | Multimedia Card (MMC)/Secure Digital (SD) Card Controller | 45 |

Submit Documentation Feedback |

|

|