www.ti.com

Peripheral Architecture

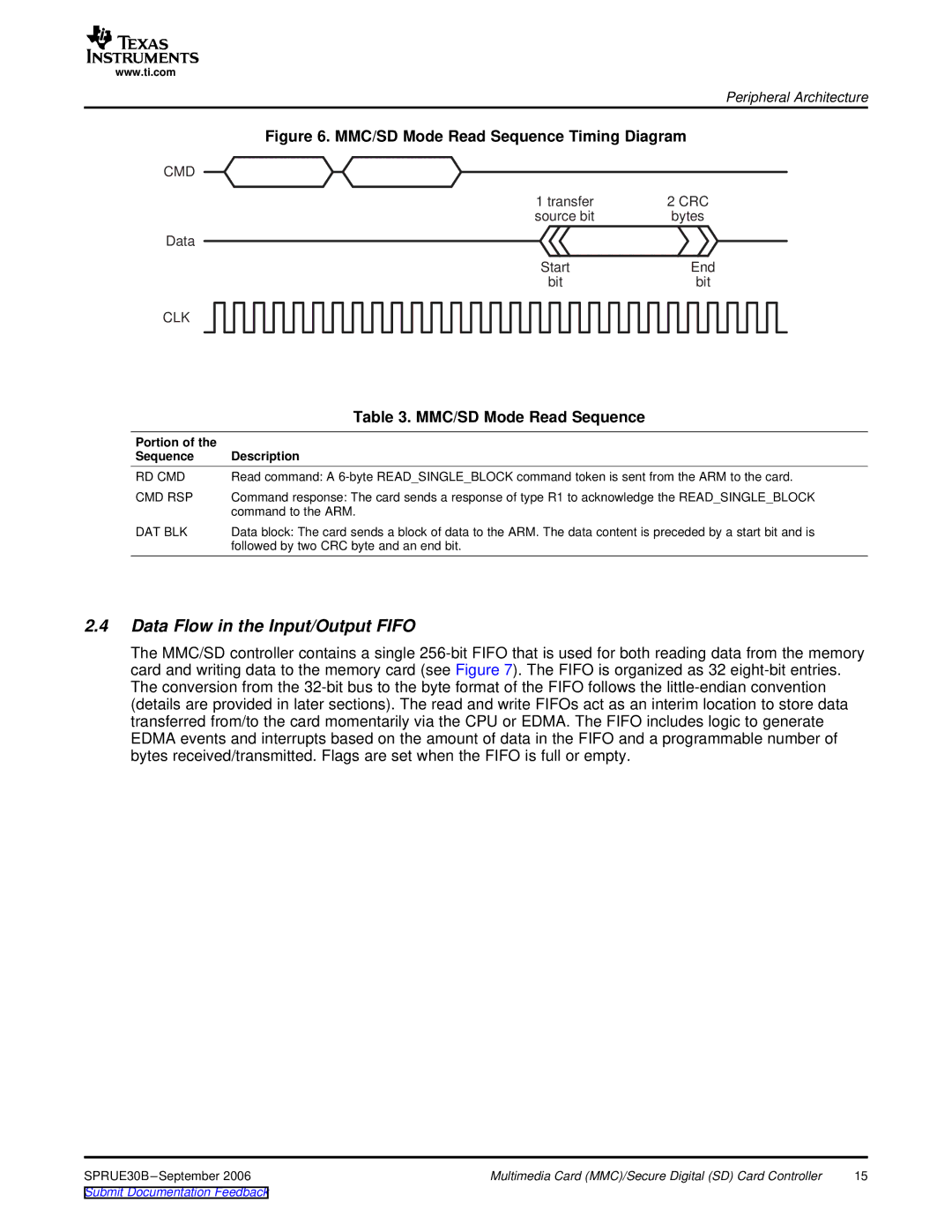

Figure 6. MMC/SD Mode Read Sequence Timing Diagram

CMD |

|

1 transfer | 2 CRC |

source bit | bytes |

Data |

|

Start | End |

bit | bit |

CLK

| Table 3. MMC/SD Mode Read Sequence |

Portion of the |

|

Sequence | Description |

RD CMD | Read command: A |

CMD RSP | Command response: The card sends a response of type R1 to acknowledge the READ_SINGLE_BLOCK |

| command to the ARM. |

DAT BLK | Data block: The card sends a block of data to the ARM. The data content is preceded by a start bit and is |

| followed by two CRC byte and an end bit. |

2.4Data Flow in the Input/Output FIFO

The MMC/SD controller contains a single

SPRUE30B | Multimedia Card (MMC)/Secure Digital (SD) Card Controller | 15 |