TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999

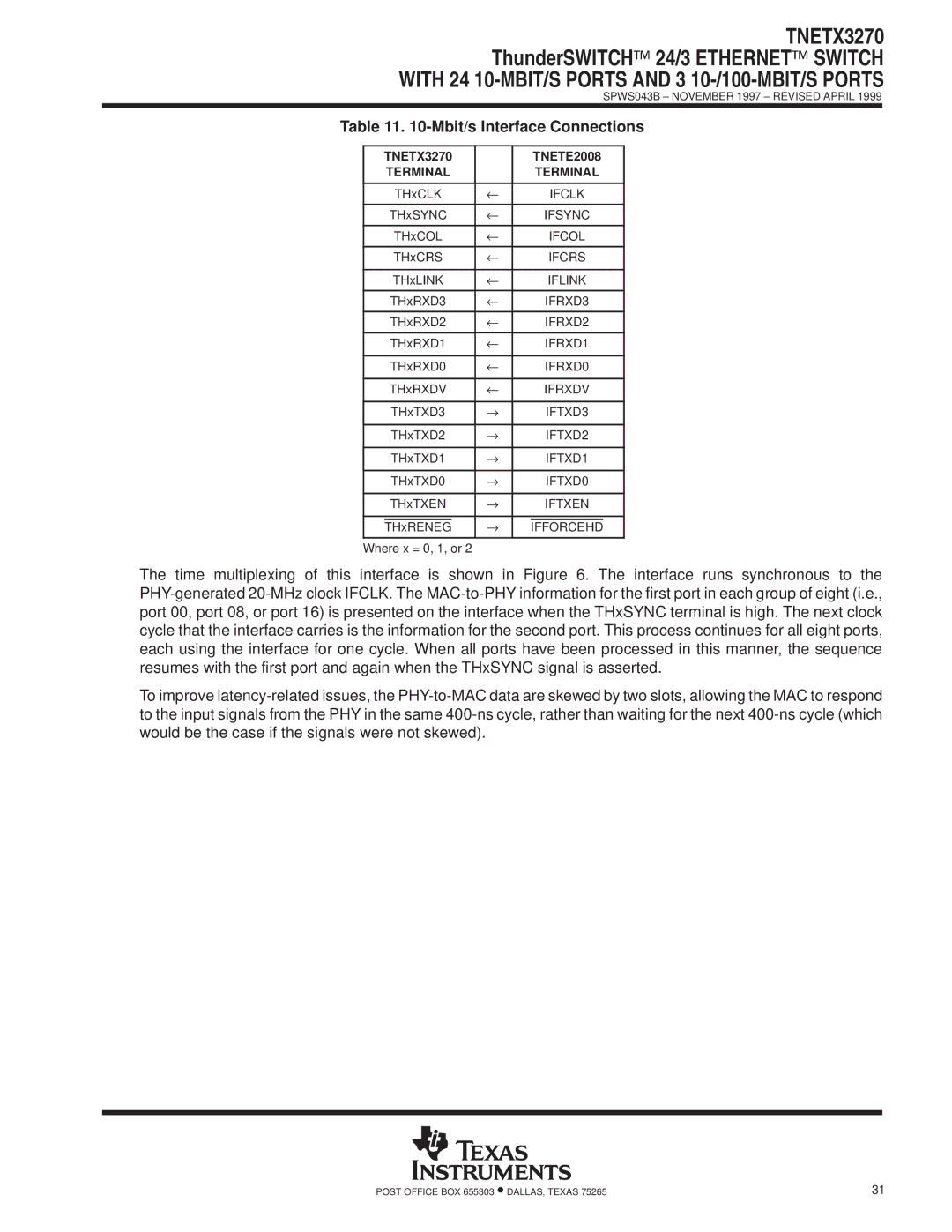

Table 11. 10-Mbit/s Interface Connections

TNETX3270 |

|

| TNETE2008 | |||

| TERMINAL |

|

| TERMINAL | ||

|

|

|

|

|

|

|

| THxCLK | ← |

| IFCLK | ||

|

|

|

|

|

|

|

| THxSYNC | ← |

| IFSYNC | ||

|

|

|

|

|

|

|

| THxCOL | ← |

| IFCOL | ||

|

|

|

|

|

|

|

| THxCRS | ← |

| IFCRS | ||

|

|

|

|

|

|

|

| THxLINK | ← |

| IFLINK | ||

|

|

|

|

|

|

|

| THxRXD3 | ← |

| IFRXD3 | ||

|

|

|

|

|

|

|

| THxRXD2 | ← |

| IFRXD2 | ||

|

|

|

|

|

|

|

| THxRXD1 | ← |

| IFRXD1 | ||

|

|

|

|

|

|

|

| THxRXD0 | ← |

| IFRXD0 | ||

|

|

|

|

|

|

|

| THxRXDV | ← |

| IFRXDV | ||

|

|

|

|

|

|

|

| THxTXD3 | → |

| IFTXD3 | ||

|

|

|

|

|

|

|

| THxTXD2 | → |

| IFTXD2 | ||

|

|

|

|

|

|

|

| THxTXD1 | → |

| IFTXD1 | ||

|

|

|

|

|

|

|

| THxTXD0 | → |

| IFTXD0 | ||

|

|

|

|

|

|

|

| THxTXEN | → |

| IFTXEN | ||

|

|

|

|

| ||

|

|

| → |

|

|

|

| THxRENEG |

|

| IFFORCEHD |

| |

|

|

|

|

| ||

Where x = 0, 1, or 2 |

|

|

|

| ||

The time multiplexing of this interface is shown in Figure 6. The interface runs synchronous to the

To improve

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 31 |