TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999

|

|

|

|

|

|

|

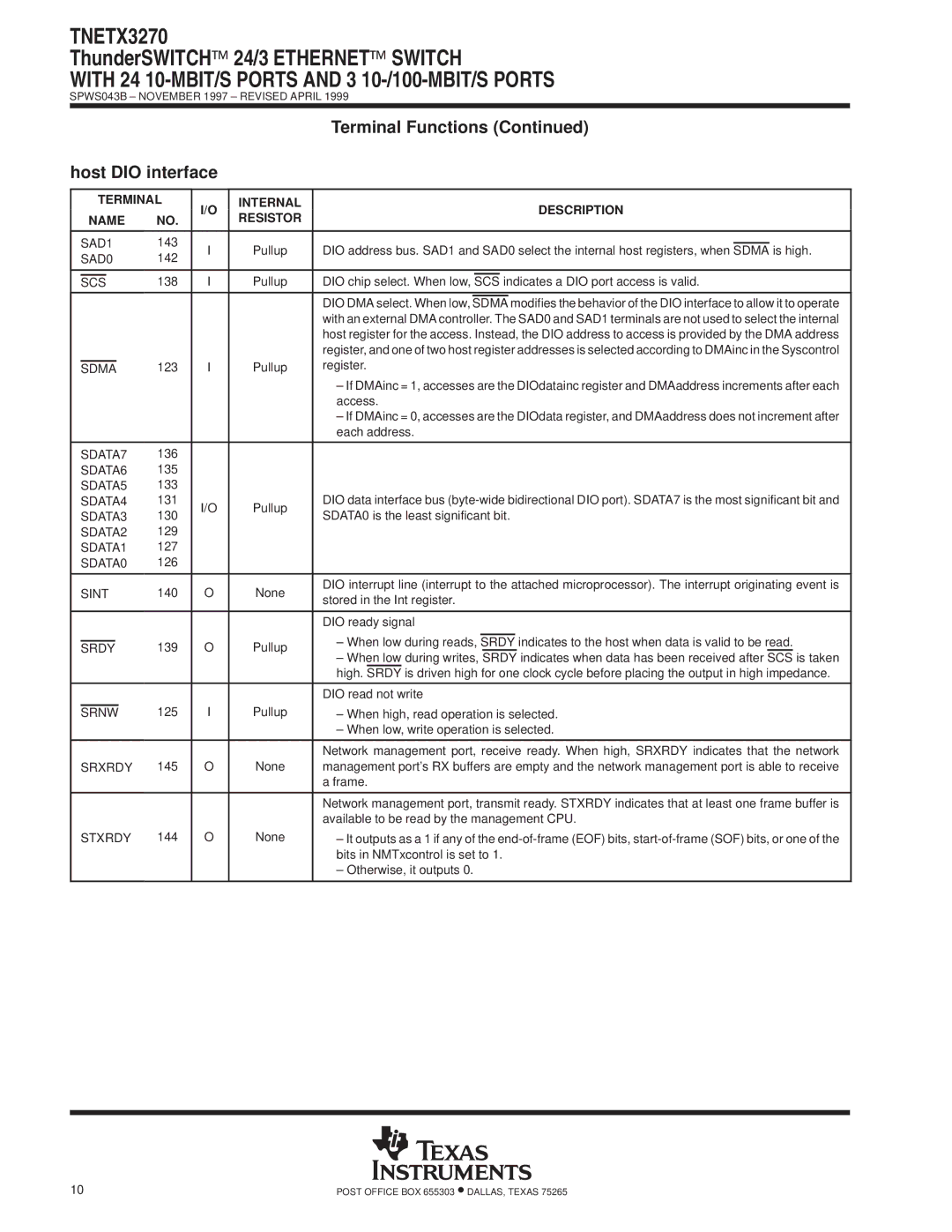

| Terminal Functions (Continued) | |||||||||

host DIO interface |

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| TERMINAL | I/O | INTERNAL |

|

|

|

|

|

| DESCRIPTION | |||||||

| NAME | NO. | RESISTOR |

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| SAD1 | 143 |

|

|

|

|

|

|

|

|

|

|

| ||||

I | Pullup | DIO address bus. SAD1 and SAD0 select the internal host registers, when SDMA is high. | |||||||||||||||

| SAD0 | 142 | |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

| 138 | I | Pullup | DIO chip select. When low, |

|

| indicates a DIO port access is valid. | ||||||

| SCS |

|

|

| SCS | ||||||||||||

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

| DIO DMA select. When low, |

|

|

|

| modifies the behavior of the DIO interface to allow it to operate | ||||

|

|

|

|

|

|

|

| SDMA | |||||||||

|

|

|

|

|

|

|

| with an external DMA controller. The SAD0 and SAD1 terminals are not used to select the internal | |||||||||

|

|

|

|

|

|

|

| host register for the access. Instead, the DIO address to access is provided by the DMA address | |||||||||

|

|

|

|

|

|

|

| register, and one of two host register addresses is selected according to DMAinc in the Syscontrol | |||||||||

|

|

|

| 123 | I | Pullup | register. | ||||||||||

| SDMA |

|

| ||||||||||||||

|

|

|

|

|

|

|

| ± If DMAinc = 1, accesses are the DIOdatainc register and DMAaddress increments after each | |||||||||

|

|

|

|

|

|

|

| access. | |||||||||

|

|

|

|

|

|

|

| ± If DMAinc = 0, accesses are the DIOdata register, and DMAaddress does not increment after | |||||||||

|

|

|

|

|

|

|

| each address. | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| SDATA7 | 136 |

|

|

|

|

|

|

|

|

|

|

| ||||

| SDATA6 | 135 |

|

|

|

|

|

|

|

|

|

|

| ||||

| SDATA5 | 133 |

|

| DIO data interface bus | ||||||||||||

| SDATA4 | 131 | I/O | Pullup | |||||||||||||

| SDATA3 | 130 | SDATA0 is the least significant bit. | ||||||||||||||

|

|

| |||||||||||||||

| SDATA2 | 129 |

|

|

|

|

|

|

|

|

|

|

| ||||

| SDATA1 | 127 |

|

|

|

|

|

|

|

|

|

|

| ||||

| SDATA0 | 126 |

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| |||||||

| SINT | 140 | O | None | DIO interrupt line (interrupt to the attached microprocessor). The interrupt originating event is | ||||||||||||

| stored in the Int register. | ||||||||||||||||

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

| DIO ready signal | |||||||||

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| 139 | O | Pullup | ± When low during reads, | SRDY | indicates to the host when data is valid to be read. | |||||||

| SRDY | ||||||||||||||||

| ± When low during writes, SRDY indicates when data has been received after SCS is taken | ||||||||||||||||

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

| high. SRDY is driven high for one clock cycle before placing the output in high impedance. | |||||||||

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

| DIO read not write | |||||||||

|

| 125 | I | Pullup |

| ||||||||||||

| SRNW |

| ± When high, read operation is selected. | ||||||||||||||

|

|

|

|

|

|

|

| ± When low, write operation is selected. | |||||||||

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

| Network management port, receive ready. When high, SRXRDY indicates that the network | |||||||||

| SRXRDY | 145 | O | None | management port's RX buffers are empty and the network management port is able to receive | ||||||||||||

|

|

|

|

|

|

|

| a frame. | |||||||||

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

| Network management port, transmit ready. STXRDY indicates that at least one frame buffer is | |||||||||

|

|

|

|

|

|

|

| available to be read by the management CPU. | |||||||||

| STXRDY | 144 | O | None | ± It outputs as a 1 if any of the | ||||||||||||

|

|

|

|

|

|

|

| bits in NMTxcontrol is set to 1. | |||||||||

|

|

|

|

|

|

|

| ± Otherwise, it outputs 0. | |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

10 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |