TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999

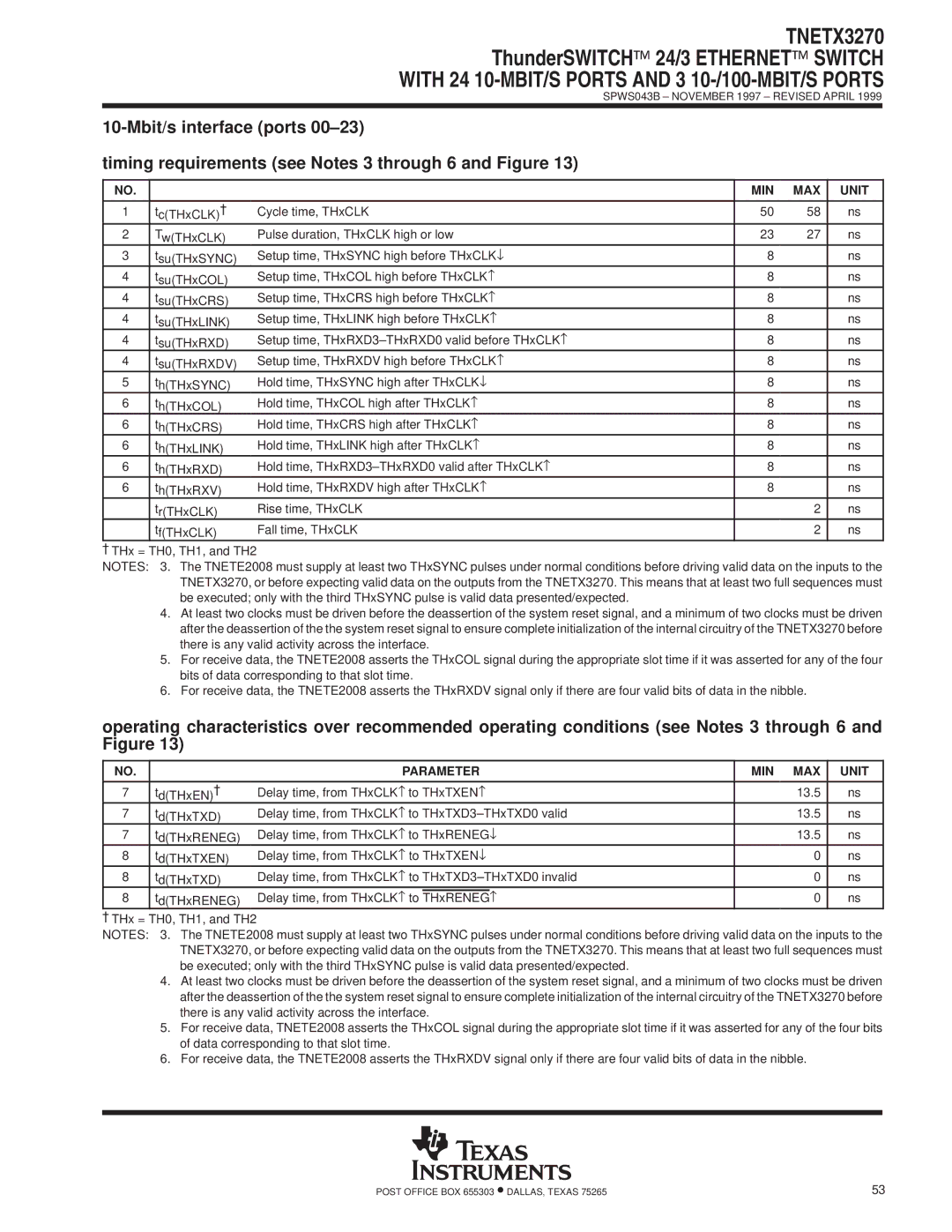

timing requirements (see Notes 3 through 6 and Figure 13)

NO. |

|

| MIN | MAX | UNIT |

|

|

|

|

|

|

1 | tc(THxCLK)² | Cycle time, THxCLK | 50 | 58 | ns |

2 | Tw(THxCLK) | Pulse duration, THxCLK high or low | 23 | 27 | ns |

3 | tsu(THxSYNC) | Setup time, THxSYNC high before THxCLK↓ | 8 |

| ns |

4 | tsu(THxCOL) | Setup time, THxCOL high before THxCLK↑ | 8 |

| ns |

4 | tsu(THxCRS) | Setup time, THxCRS high before THxCLK↑ | 8 |

| ns |

4 | tsu(THxLINK) | Setup time, THxLINK high before THxCLK↑ | 8 |

| ns |

4 | tsu(THxRXD) | Setup time, THxRXD3±THxRXD0 valid before THxCLK↑ | 8 |

| ns |

4 | tsu(THxRXDV) | Setup time, THxRXDV high before THxCLK↑ | 8 |

| ns |

5 | th(THxSYNC) | Hold time, THxSYNC high after THxCLK↓ | 8 |

| ns |

6 | th(THxCOL) | Hold time, THxCOL high after THxCLK↑ | 8 |

| ns |

6 | th(THxCRS) | Hold time, THxCRS high after THxCLK↑ | 8 |

| ns |

6 | th(THxLINK) | Hold time, THxLINK high after THxCLK↑ | 8 |

| ns |

6 | th(THxRXD) | Hold time, THxRXD3±THxRXD0 valid after THxCLK↑ | 8 |

| ns |

6 | th(THxRXV) | Hold time, THxRXDV high after THxCLK↑ | 8 |

| ns |

| tr(THxCLK) | Rise time, THxCLK |

| 2 | ns |

| tf(THxCLK) | Fall time, THxCLK |

| 2 | ns |

² THx = TH0, TH1, and TH2

NOTES: 3. The TNETE2008 must supply at least two THxSYNC pulses under normal conditions before driving valid data on the inputs to the TNETX3270, or before expecting valid data on the outputs from the TNETX3270. This means that at least two full sequences must be executed; only with the third THxSYNC pulse is valid data presented/expected.

4.At least two clocks must be driven before the deassertion of the system reset signal, and a minimum of two clocks must be driven after the deassertion of the the system reset signal to ensure complete initialization of the internal circuitry of the TNETX3270 before there is any valid activity across the interface.

5.For receive data, the TNETE2008 asserts the THxCOL signal during the appropriate slot time if it was asserted for any of the four bits of data corresponding to that slot time.

6.For receive data, the TNETE2008 asserts the THxRXDV signal only if there are four valid bits of data in the nibble.

operating characteristics over recommended operating conditions (see Notes 3 through 6 and Figure 13)

NO. |

| PARAMETER | MIN MAX | UNIT | ||

|

|

|

|

|

|

|

7 | td(THxEN)² | Delay time, from THxCLK↑ to THxTXEN↑ | 13.5 | ns | ||

7 | td(THxTXD) | Delay time, from THxCLK↑ to THxTXD3±THxTXD0 valid | 13.5 | ns | ||

7 | td(THxRENEG) | Delay time, from THxCLK↑ to THxRENEG↓ | 13.5 | ns | ||

8 | td(THxTXEN) | Delay time, from THxCLK↑ to THxTXEN↓ | 0 | ns | ||

8 | td(THxTXD) | Delay time, from THxCLK↑ to THxTXD3±THxTXD0 invalid | 0 | ns | ||

8 | td(THxRENEG) | Delay time, from THxCLK↑ to |

| ↑ | 0 | ns |

THxRENEG | ||||||

² THx = TH0, TH1, and TH2

NOTES: 3. The TNETE2008 must supply at least two THxSYNC pulses under normal conditions before driving valid data on the inputs to the TNETX3270, or before expecting valid data on the outputs from the TNETX3270. This means that at least two full sequences must be executed; only with the third THxSYNC pulse is valid data presented/expected.

4.At least two clocks must be driven before the deassertion of the system reset signal, and a minimum of two clocks must be driven after the deassertion of the the system reset signal to ensure complete initialization of the internal circuitry of the TNETX3270 before there is any valid activity across the interface.

5.For receive data, TNETE2008 asserts the THxCOL signal during the appropriate slot time if it was asserted for any of the four bits of data corresponding to that slot time.

6.For receive data, the TNETE2008 asserts the THxRXDV signal only if there are four valid bits of data in the nibble.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 53 |