TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999

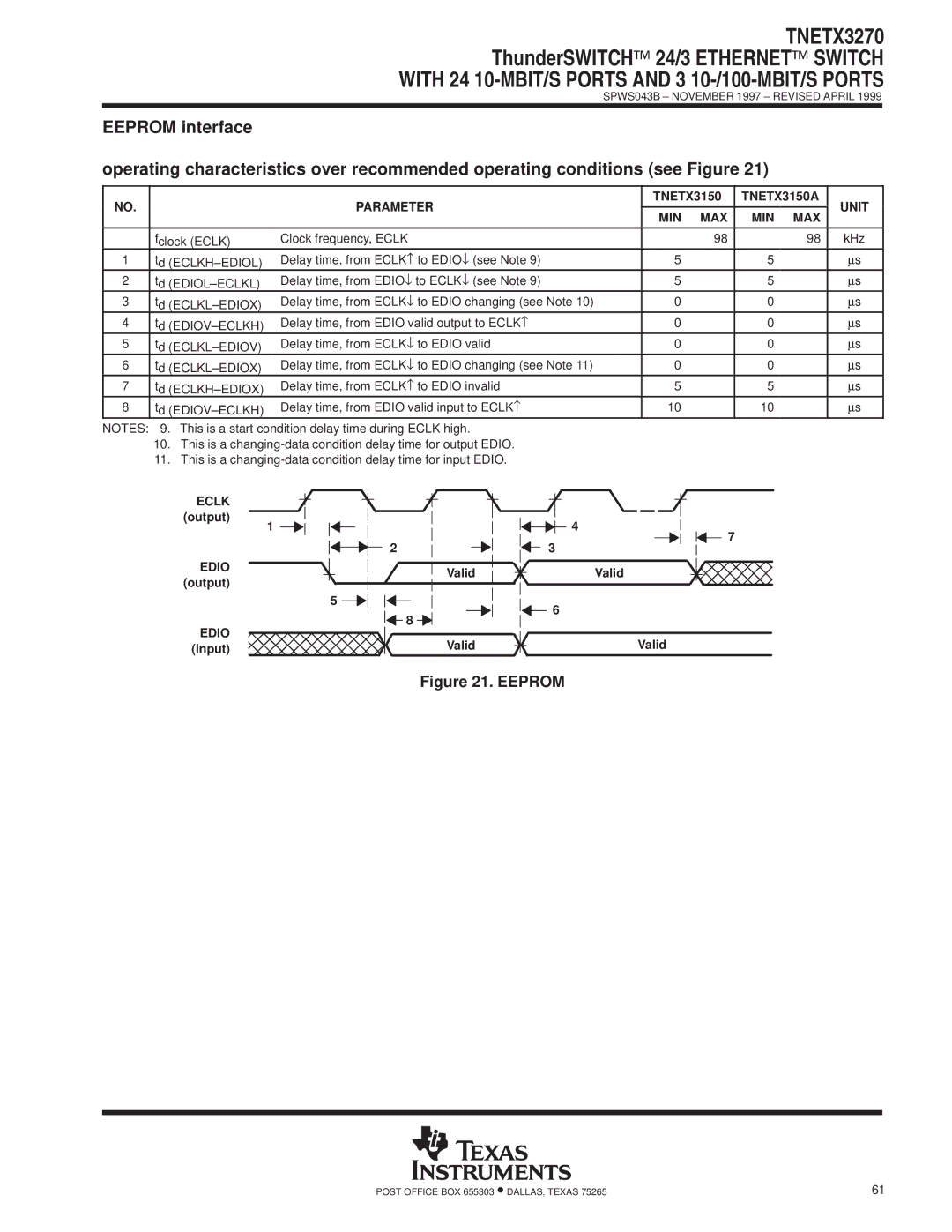

EEPROM interface

operating characteristics over recommended operating conditions (see Figure 21)

NO. |

| PARAMETER | TNETX3150 | TNETX3150A | UNIT |

|

|

| |||

| MIN MAX | MIN MAX | |||

|

|

|

| ||

|

|

|

|

|

|

| fclock (ECLK) | Clock frequency, ECLK | 98 | 98 | kHz |

1 | td (ECLKH±EDIOL) | Delay time, from ECLK↑ to EDIO↓ (see Note 9) | 5 | 5 | μs |

2 | td (EDIOL±ECLKL) | Delay time, from EDIO↓ to ECLK↓ (see Note 9) | 5 | 5 | μs |

3 | td (ECLKL±EDIOX) | Delay time, from ECLK↓ to EDIO changing (see Note 10) | 0 | 0 | μs |

4 | td (EDIOV±ECLKH) | Delay time, from EDIO valid output to ECLK↑ | 0 | 0 | μs |

5 | td (ECLKL±EDIOV) | Delay time, from ECLK↓ to EDIO valid | 0 | 0 | μs |

6 | td (ECLKL±EDIOX) | Delay time, from ECLK↓ to EDIO changing (see Note 11) | 0 | 0 | μs |

7 | td (ECLKH±EDIOX) | Delay time, from ECLK↑ to EDIO invalid | 5 | 5 | μs |

8 | td (EDIOV±ECLKH) | Delay time, from EDIO valid input to ECLK↑ | 10 | 10 | μs |

NOTES: 9. This is a start condition delay time during ECLK high.

10.This is a

11.This is a

ECLK

(output)

1

EDIO (output)

EDIO (input)

2

Valid

5

![]() 8

8 ![]()

Valid

4

7

3

Valid

6

Valid

Figure 21. EEPROM

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 61 |