TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999

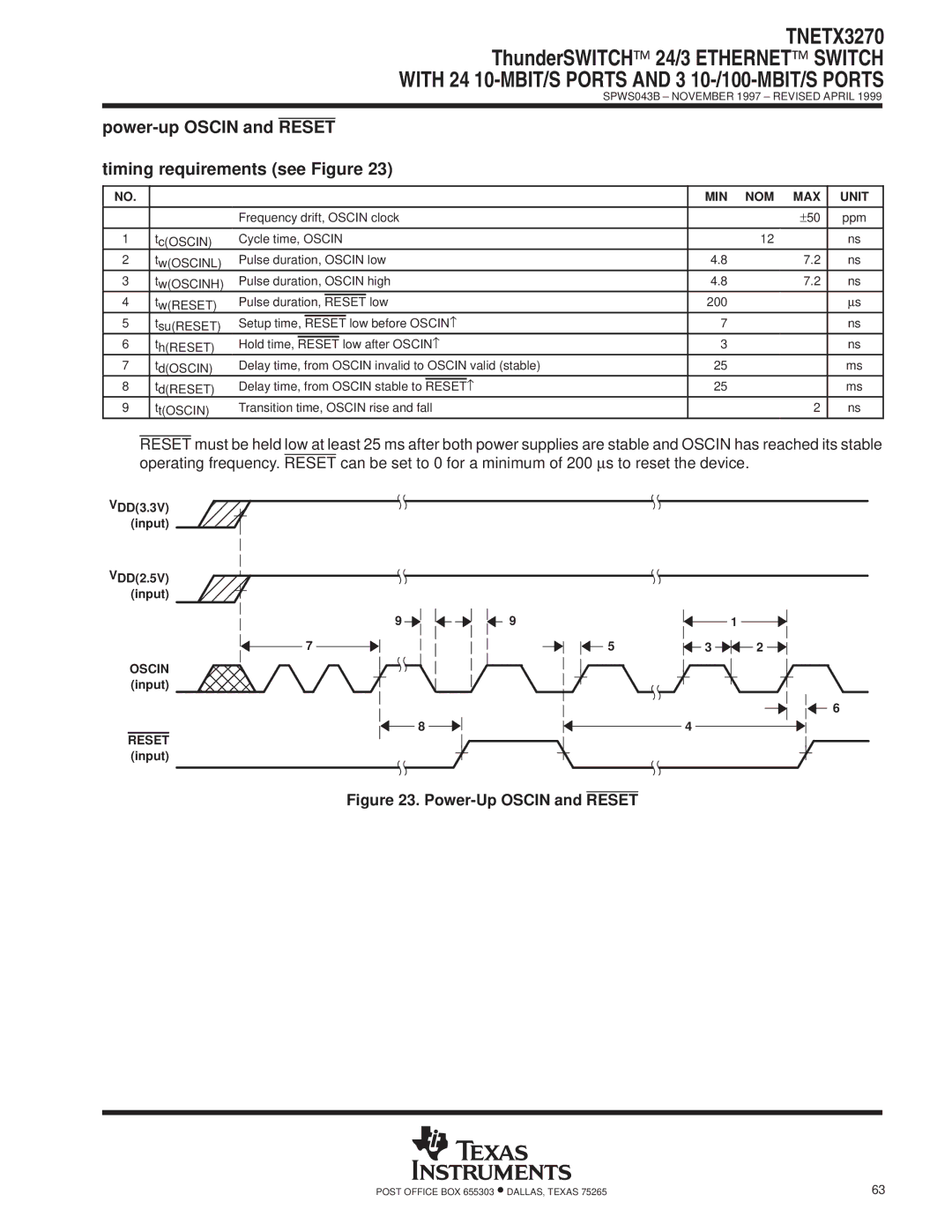

power-up OSCIN and RESET

timing requirements (see Figure 23)

NO. |

|

|

|

|

|

|

|

|

|

| MIN NOM | MAX | UNIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Frequency drift, OSCIN clock |

| ±50 | ppm | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 | tc(OSCIN) | Cycle time, OSCIN | 12 |

| ns | ||||||||

2 | tw(OSCINL) | Pulse duration, OSCIN low | 4.8 | 7.2 | ns | ||||||||

3 | tw(OSCINH) | Pulse duration, OSCIN high | 4.8 | 7.2 | ns | ||||||||

4 | tw(RESET) | Pulse duration, |

|

|

| low | 200 |

| μs | ||||

RESET |

| ||||||||||||

5 | tsu(RESET) | Setup time, |

|

|

| low before OSCIN↑ | 7 |

| ns | ||||

RESET |

| ||||||||||||

6 | th(RESET) | Hold time, |

|

|

| low after OSCIN↑ | 3 |

| ns | ||||

RESET |

| ||||||||||||

7 | td(OSCIN) | Delay time, from OSCIN invalid to OSCIN valid (stable) | 25 |

| ms | ||||||||

8 | td(RESET) | Delay time, from OSCIN stable to |

| ↑ | 25 |

| ms | ||||||

RESET |

| ||||||||||||

9 | tt(OSCIN) | Transition time, OSCIN rise and fall |

| 2 | ns | ||||||||

RESET must be held low at least 25 ms after both power supplies are stable and OSCIN has reached its stable operating frequency. RESET can be set to 0 for a minimum of 200 μs to reset the device.

VDD(3.3V) (input)

VDD(2.5V) (input)

9 | 9 |

|

| 1 |

7 |

| 5 | 3 | 2 |

OSCIN (input)

6

8 | 4 |

RESET (input)

Figure 23. Power-Up OSCIN and RESET

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 63 |