TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999

receive versus transmit priority

The queue manager prioritizes receive and transmit traffic as follows:

DHighest priority is given to frames that currently are being transmitted. This ensures that transmitting frames do not underrun.

DNext priority is given to frames that are received if the

DLowest priority is given to frames that are queued for transmission but have not yet started to transmit. These frames are promoted to the highest priority only when there is spare capacity on the memory bus.

DThe NM port receives the lowest priority to prevent frame loss during busy periods.

The memory bus has enough bandwidth to support the two highest priorities. The untransmitted frame queues grow when frames received on different ports require transmission on the same port(s) and when frames are repeatedly received on ports that are at a higher speed than the ports on which they are transmitted. This is likely to be exacerbated by the reception of multicast frames, which typically require transmission on several ports. When the backlog grows to such an extent that the free buffer stack is nearly empty, flow control is initiated (if it has been enabled) to limit further frame reception.

uplink pretagging

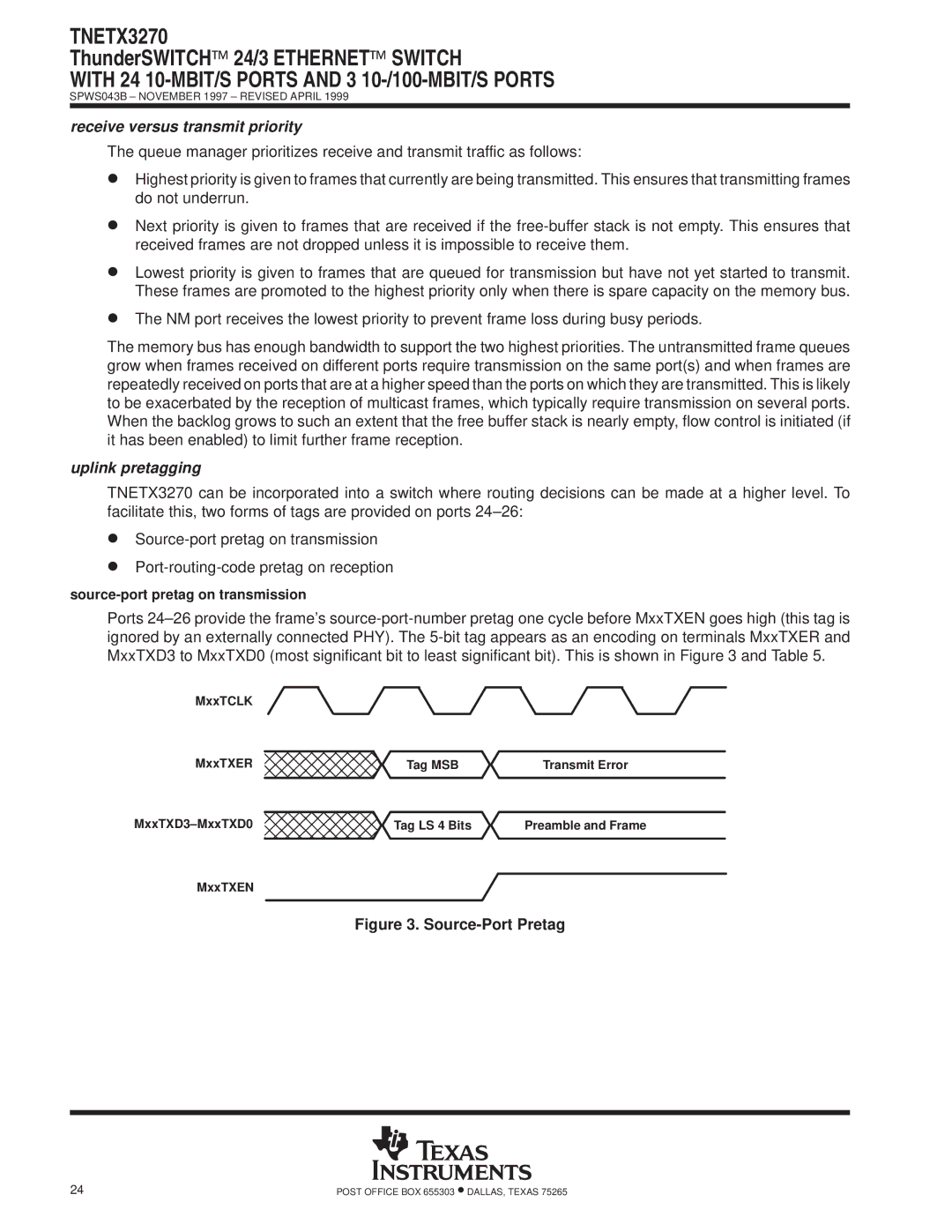

TNETX3270 can be incorporated into a switch where routing decisions can be made at a higher level. To facilitate this, two forms of tags are provided on ports 24±26:

D

D

Ports 24±26 provide the frame's

MxxTCLK |

|

|

MxxTXER | Tag MSB | Transmit Error |

MxxTXD3±MxxTXD0 | Tag LS 4 Bits | Preamble and Frame |

MxxTXEN

Figure 3. Source-Port Pretag

24 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |