TNETX3270

ThunderSWITCH 24/3 ETHERNET SWITCH

WITH 24 10-MBIT/S PORTS AND 3 10-/100-MBIT/S PORTS

SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999

DIO/DMA interface

The DIO interface is asynchronous to allow easy adaptation to a range of microprocessor devices and computer system interfaces.

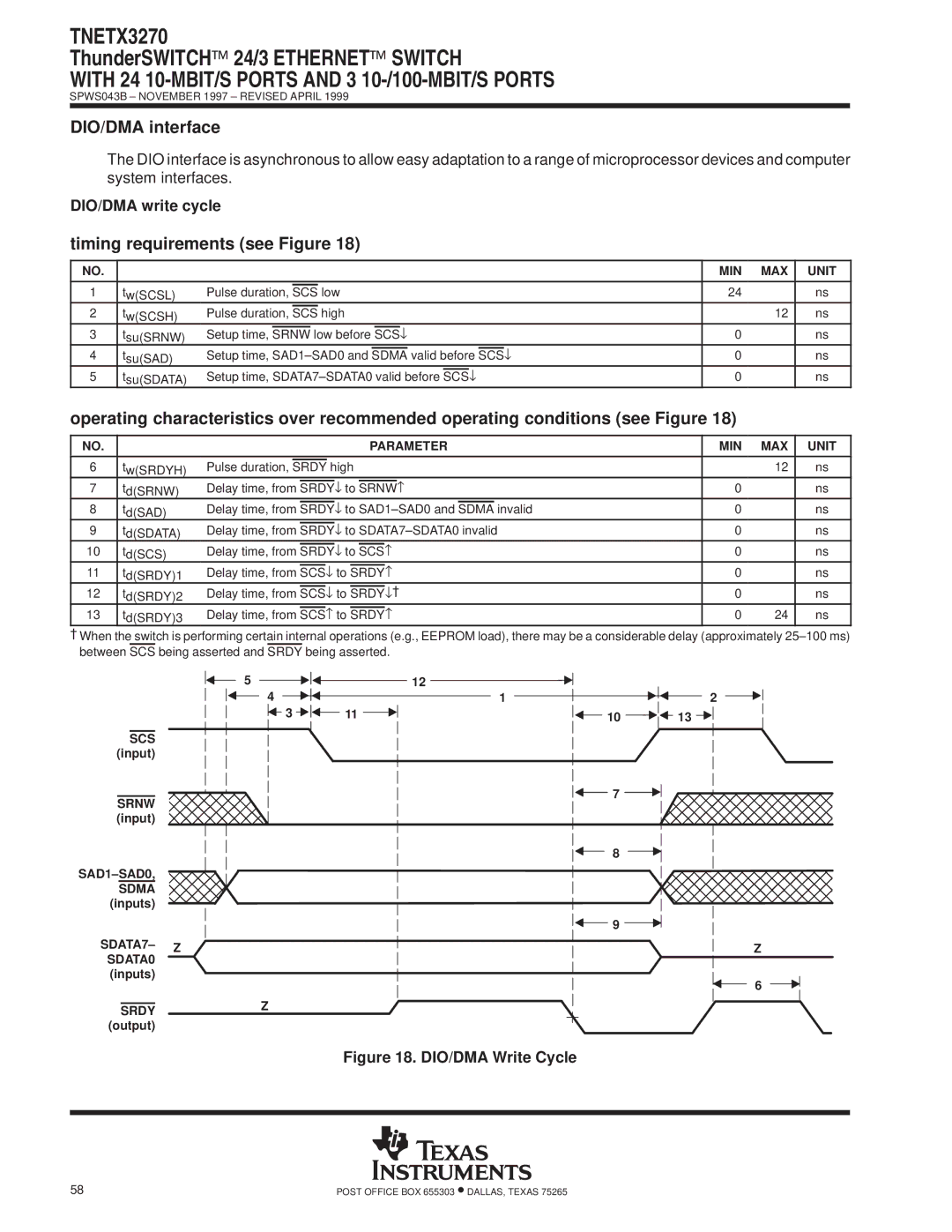

DIO/DMA write cycle

timing requirements (see Figure 18)

NO. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MIN MAX | UNIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

1 | tw(SCSL) | Pulse duration, |

|

|

| low | 24 | ns | ||||||||||

SCS |

| |||||||||||||||||

2 | tw(SCSH) | Pulse duration, |

|

|

|

| high | 12 | ns | |||||||||

SCS | ||||||||||||||||||

3 | tsu(SRNW) | Setup time, |

|

|

| low before |

| ↓ | 0 | ns | ||||||||

SRNW | SCS | |||||||||||||||||

4 | tsu(SAD) | Setup time, SAD1±SAD0 and |

|

|

| valid before |

| ↓ | 0 | ns | ||||||||

SDMA | SCS | |||||||||||||||||

5 | tsu(SDATA) | Setup time, SDATA7±SDATA0 valid before |

| ↓ | 0 | ns | ||||||||||||

SCS | ||||||||||||||||||

operating characteristics over recommended operating conditions (see Figure 18)

NO. |

|

|

|

|

|

|

|

|

|

|

| PARAMETER | MIN | MAX | UNIT | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

6 | tw(SRDYH) | Pulse duration, |

|

|

|

|

| high |

| 12 | ns | |||||||||

SRDY |

| |||||||||||||||||||

7 | td(SRNW) | Delay time, from |

|

|

|

| ↓ to |

|

|

| ↑ | 0 |

| ns | ||||||

SRDY | SRNW |

| ||||||||||||||||||

8 | td(SAD) | Delay time, from |

|

|

|

|

| ↓ to SAD1±SAD0 and |

| invalid | 0 |

| ns | |||||||

SRDY | SDMA |

| ||||||||||||||||||

9 | td(SDATA) | Delay time, from |

|

|

|

|

| ↓ to SDATA7±SDATA0 invalid | 0 |

| ns | |||||||||

SRDY |

| |||||||||||||||||||

10 | td(SCS) | Delay time, from |

|

|

|

|

| ↓ to |

| ↑ | 0 |

| ns | |||||||

SRDY | SCS |

| ||||||||||||||||||

11 | td(SRDY)1 | Delay time, from |

| ↓ to |

|

|

| ↑ | 0 |

| ns | |||||||||

SCS | SRDY |

| ||||||||||||||||||

12 | t | Delay time, from |

|

|

| ↓ to |

|

|

| ↓² | 0 |

| ns | |||||||

SCS | SRDY |

| ||||||||||||||||||

| d(SRDY)2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 | td(SRDY)3 | Delay time, from |

|

| ↑ to |

|

|

| ↑ | 0 | 24 | ns | ||||||||

SCS | SRDY | |||||||||||||||||||

²When the switch is performing certain internal operations (e.g., EEPROM load), there may be a considerable delay (approximately 25±100 ms) between SCS being asserted and SRDY being asserted.

5 |

| 12 |

|

4 |

| 1 | 2 |

3 | 11 | 10 | 13 |

SCS (input)

7

SRNW (input)

8

SAD1±SAD0,

SDMA (inputs)

| 9 |

SDATA7± Z | Z |

SDATA0 |

|

(inputs) | 6 |

| |

SRDY | Z |

| |

(output) |

|

Figure 18. DIO/DMA Write Cycle

58 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |