|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TNETX3270 | |

|

|

|

|

|

|

|

|

| ThunderSWITCH 24/3 ETHERNET SWITCH | |||||||||||||||||

|

|

|

|

|

|

| WITH 24 | |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SPWS043B ± NOVEMBER 1997 ± REVISED APRIL 1999 | |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Terminal Functions (Continued) | |||||||||||||||||||

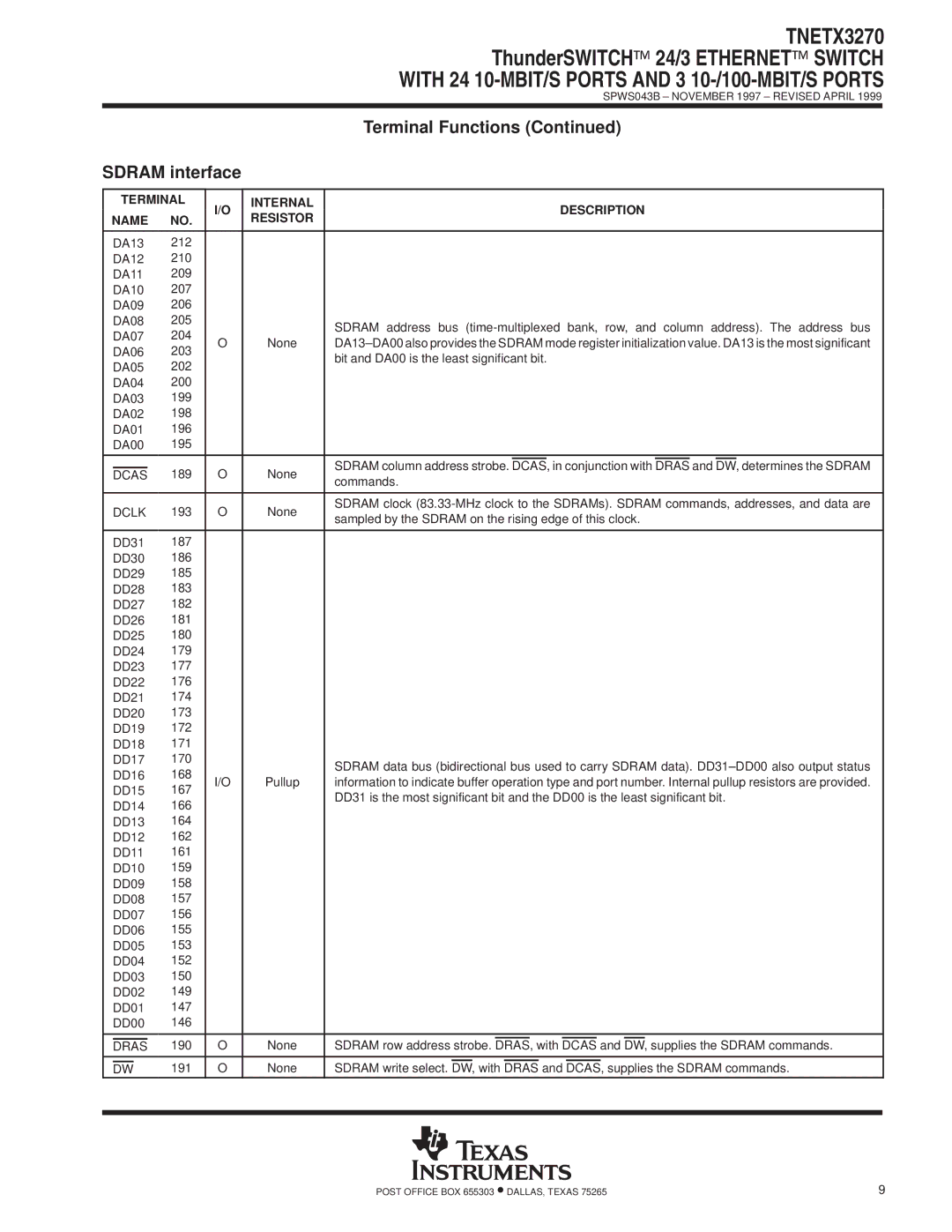

SDRAM interface |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| TERMINAL | I/O | INTERNAL |

|

|

|

|

|

|

|

| DESCRIPTION |

| |||||||||||||

NAME | NO. | RESISTOR |

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DA13 | 212 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA12 | 210 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA11 | 209 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA10 | 207 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA09 | 206 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA08 | 205 |

|

| SDRAM address bus |

| ||||||||||||||||||||

| DA07 | 204 |

|

|

| |||||||||||||||||||||

| O | None | DA13±DA00 also provides the SDRAM mode register initialization value. DA13 is the most significant |

| ||||||||||||||||||||||

| DA06 | 203 |

| |||||||||||||||||||||||

|

|

| bit and DA00 is the least significant bit. |

| ||||||||||||||||||||||

| DA05 | 202 |

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| DA04 | 200 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA03 | 199 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA02 | 198 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA01 | 196 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DA00 | 195 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

| SDRAM column address strobe. |

|

|

| in conjunction with |

| and |

| determines the SDRAM |

| ||||||||||

|

|

|

| 189 | O | None | DCAS, | DRAS | DW, |

| ||||||||||||||||

| DCAS | |||||||||||||||||||||||||

| commands. |

| ||||||||||||||||||||||||

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| DCLK | 193 | O | None | SDRAM clock |

| ||||||||||||||||||||

| sampled by the SDRAM on the rising edge of this clock. |

| ||||||||||||||||||||||||

|

|

|

|

|

|

|

| |||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| DD31 | 187 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD30 | 186 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD29 | 185 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD28 | 183 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD27 | 182 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD26 | 181 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD25 | 180 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD24 | 179 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD23 | 177 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD22 | 176 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD21 | 174 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD20 | 173 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD19 | 172 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD18 | 171 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD17 | 170 |

|

| SDRAM data bus (bidirectional bus used to carry SDRAM data). DD31±DD00 also output status |

| ||||||||||||||||||||

| DD16 | 168 |

|

|

| |||||||||||||||||||||

| I/O | Pullup | information to indicate buffer operation type and port number. Internal pullup resistors are provided. |

| ||||||||||||||||||||||

| DD15 | 167 |

| |||||||||||||||||||||||

|

|

| DD31 is the most significant bit and the DD00 is the least significant bit. |

| ||||||||||||||||||||||

| DD14 | 166 |

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| DD13 | 164 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD12 | 162 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD11 | 161 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD10 | 159 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD09 | 158 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD08 | 157 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD07 | 156 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD06 | 155 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD05 | 153 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD04 | 152 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD03 | 150 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD02 | 149 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD01 | 147 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| DD00 | 146 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

| 190 | O | None | SDRAM row address strobe. |

|

|

| with |

|

| and |

| supplies the SDRAM commands. |

| |||||||||

| DRAS |

| DRAS, | DCAS | DW, | |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

| 191 | O | None | SDRAM write select. |

| with |

|

|

| and |

|

| supplies the SDRAM commands. |

| |||||||||

| DW |

| DW, | DRAS | DCAS, | |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 9 |