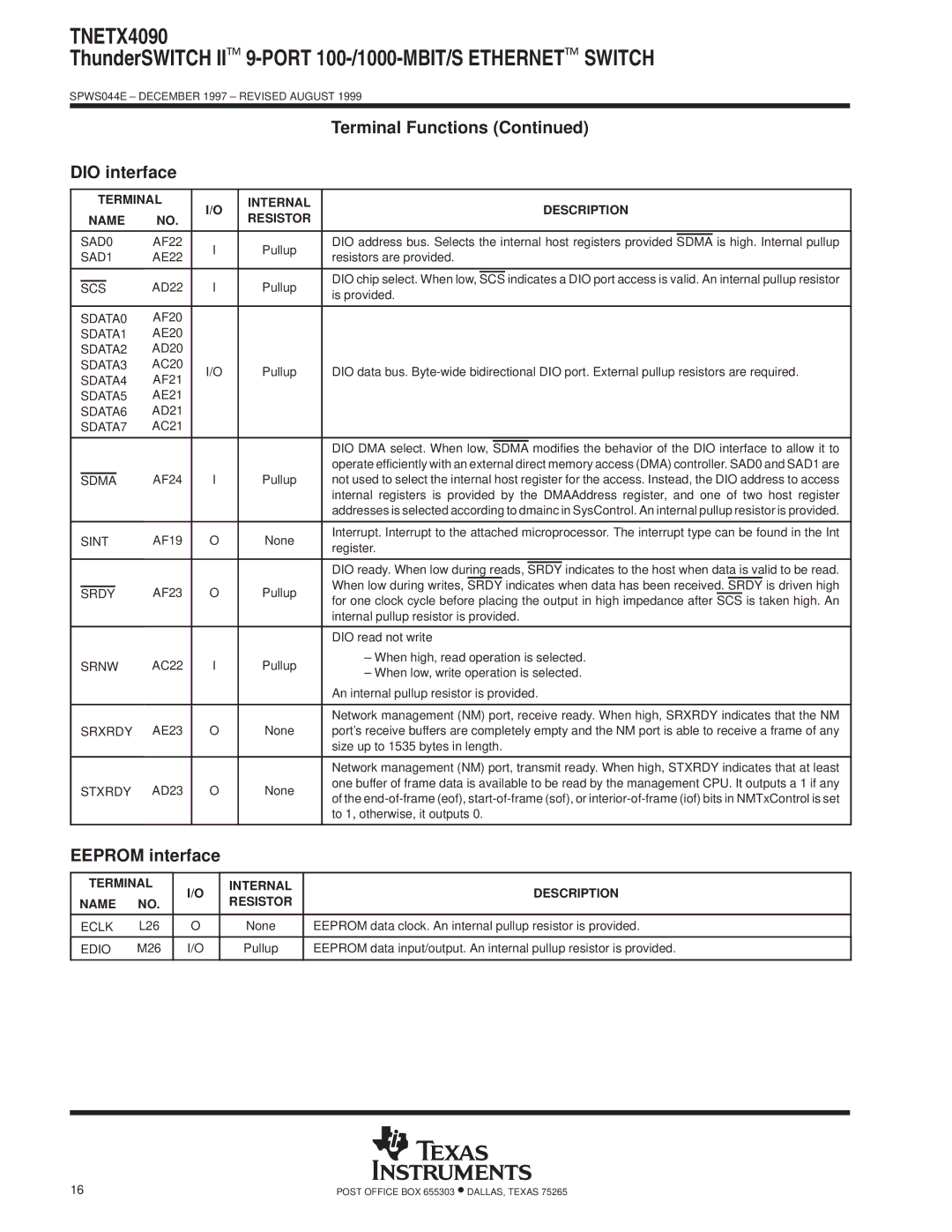

TNETX4090

ThunderSWITCH II 9-PORT 100-/1000-MBIT/S ETHERNET SWITCH

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

|

|

|

|

|

|

|

|

|

|

|

|

| Terminal Functions (Continued) | ||||||||

DIO interface |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| TERMINAL |

| I/O |

| INTERNAL |

|

|

|

|

|

| DESCRIPTION | |||||||||

| NAME | NO. |

|

| RESISTOR |

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

| SAD0 | AF22 |

|

|

|

|

|

|

| DIO address bus. Selects the internal host registers provided |

| is high. Internal pullup | |||||||||

|

| I |

| Pullup |

| SDMA | |||||||||||||||

| SAD1 | AE22 |

|

|

| resistors are provided. | |||||||||||||||

|

|

|

|

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| DIO chip select. When low, |

|

| indicates a DIO port access is valid. An internal pullup resistor | |||||

|

|

|

| AD22 |

| I |

| Pullup |

| SCS | |||||||||||

| SCS |

|

| ||||||||||||||||||

|

|

|

| is provided. | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

| SDATA0 | AF20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| SDATA1 | AE20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| SDATA2 | AD20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| SDATA3 | AC20 |

| I/O |

| Pullup |

| DIO data bus. | |||||||||||||

| SDATA4 | AF21 |

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

| SDATA5 | AE21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| SDATA6 | AD21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| SDATA7 | AC21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

| DIO DMA select. When low, |

|

|

| modifies the behavior of the DIO interface to allow it to | ||||

|

|

|

|

|

|

|

|

|

|

|

|

| SDMA | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| operate efficiently with an external direct memory access (DMA) controller. SAD0 and SAD1 are | ||||||||

| SDMA |

| AF24 |

| I |

| Pullup |

| not used to select the internal host register for the access. Instead, the DIO address to access | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| internal registers is provided by the DMAAddress register, and one of two host register | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| addresses is selected according to dmainc in SysControl. An internal pullup resistor is provided. | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

| SINT | AF19 |

| O |

| None |

| Interrupt. Interrupt to the attached microprocessor. The interrupt type can be found in the Int | |||||||||||||

|

|

|

| register. | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| DIO ready. When low during reads, |

|

| indicates to the host when data is valid to be read. | |||||

|

|

|

|

|

|

|

|

|

|

|

|

| SRDY | ||||||||

|

|

|

| AF23 |

| O |

| Pullup |

| When low during writes, SRDY indicates when data has been received. SRDY is driven high | |||||||||||

| SRDY |

|

| ||||||||||||||||||

|

|

|

| for one clock cycle before placing the output in high impedance after SCS is taken high. An | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| internal pullup resistor is provided. | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| DIO read not write | ||||||||

| SRNW | AC22 |

| I |

| Pullup |

| ± When high, read operation is selected. | |||||||||||||

|

|

|

| ± When low, write operation is selected. | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| An internal pullup resistor is provided. | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Network management (NM) port, receive ready. When high, SRXRDY indicates that the NM | ||||||||

| SRXRDY | AE23 |

| O |

| None |

| port's receive buffers are completely empty and the NM port is able to receive a frame of any | |||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| size up to 1535 bytes in length. | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Network management (NM) port, transmit ready. When high, STXRDY indicates that at least | ||||||||

| STXRDY | AD23 |

| O |

| None |

| one buffer of frame data is available to be read by the management CPU. It outputs a 1 if any | |||||||||||||

|

|

|

| of the | |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| to 1, otherwise, it outputs 0. | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

EEPROM interface |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| TERMINAL |

| I/O |

| INTERNAL |

|

|

|

|

|

|

| DESCRIPTION | ||||||||

NAME | NO. |

|

| RESISTOR |

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||

| ECLK | L26 |

| O |

|

| None |

| EEPROM data clock. An internal pullup resistor is provided. | ||||||||||||

|

|

|

|

|

|

|

|

|

| ||||||||||||

| EDIO | M26 |

| I/O |

|

| Pullup |

| EEPROM data input/output. An internal pullup resistor is provided. | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |