TNETX4090

ThunderSWITCH II 9-PORT 100-/1000-MBIT/S ETHERNET SWITCH

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

|

|

|

|

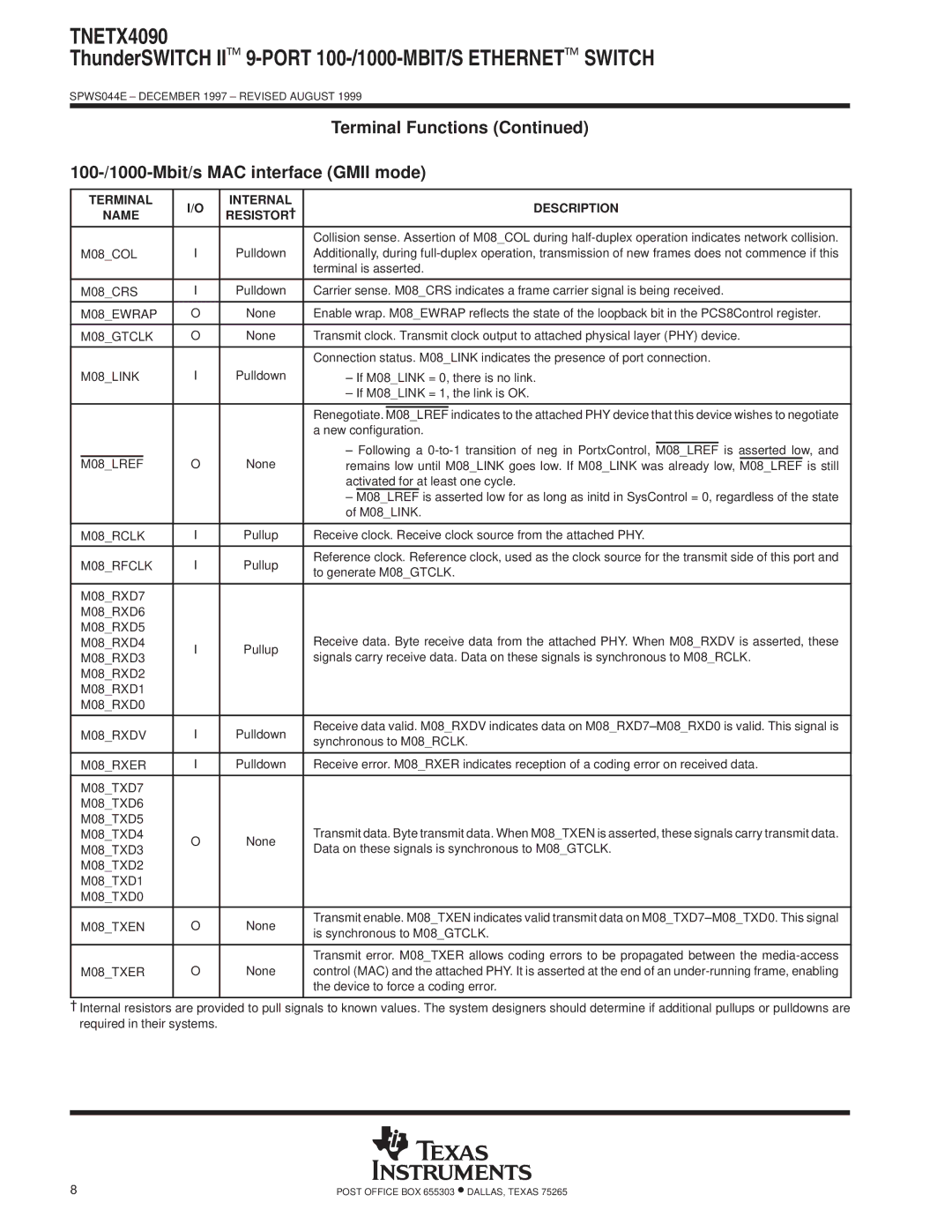

| Terminal Functions (Continued) | ||||

| |||||||||

|

|

|

|

|

|

|

|

|

|

| TERMINAL | I/O | INTERNAL |

|

| DESCRIPTION | |||

| NAME | RESISTOR² |

|

| |||||

|

|

|

|

|

|

| |||

|

|

|

|

| Collision sense. Assertion of M08_COL during | ||||

| M08_COL | I | Pulldown | Additionally, during | |||||

|

|

|

|

| terminal is asserted. | ||||

|

|

|

|

|

|

|

|

|

|

| M08_CRS | I | Pulldown | Carrier sense. M08_CRS indicates a frame carrier signal is being received. | |||||

|

|

|

|

|

|

|

|

|

|

| M08_EWRAP | O | None | Enable wrap. M08_EWRAP reflects the state of the loopback bit in the PCS8Control register. | |||||

|

|

|

|

|

|

|

|

|

|

| M08_GTCLK | O | None | Transmit clock. Transmit clock output to attached physical layer (PHY) device. | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Connection status. M08_LINK indicates the presence of port connection. | ||||

| M08_LINK | I | Pulldown | ± If M08_LINK = 0, there is no link. | |||||

|

|

|

|

| ± If M08_LINK = 1, the link is OK. | ||||

|

|

|

|

|

|

|

| ||

|

|

|

|

| Renegotiate. |

| indicates to the attached PHY device that this device wishes to negotiate | ||

|

|

|

|

| M08_LREF | ||||

|

|

|

|

| a new configuration. | ||||

|

|

|

|

|

| ||||

|

|

| O | None | ± Following a | M08_LREF | is asserted low, and | ||

| M08_LREF |

| remains low until M08_LINK goes low. If M08_LINK was already low, M08_LREF is still | ||||||

|

|

|

|

| activated for at least one cycle. | ||||

|

|

|

|

| ± M08_LREF is asserted low for as long as initd in SysControl = 0, regardless of the state | ||||

|

|

|

|

| of M08_LINK. | ||||

|

|

|

|

| |||||

| M08_RCLK | I | Pullup | Receive clock. Receive clock source from the attached PHY. | |||||

|

|

|

|

|

| ||||

| M08_RFCLK | I | Pullup | Reference clock. Reference clock, used as the clock source for the transmit side of this port and | |||||

| to generate M08_GTCLK. | ||||||||

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| |

| M08_RXD7 |

|

|

|

|

|

|

| |

| M08_RXD6 |

|

|

|

|

|

|

| |

| M08_RXD5 |

|

| Receive data. Byte receive data from the attached PHY. When M08_RXDV is asserted, these | |||||

| M08_RXD4 | I | Pullup | ||||||

| M08_RXD3 | signals carry receive data. Data on these signals is synchronous to M08_RCLK. | |||||||

|

|

| |||||||

| M08_RXD2 |

|

|

|

|

|

|

| |

| M08_RXD1 |

|

|

|

|

|

|

| |

| M08_RXD0 |

|

|

|

|

|

|

| |

|

|

|

|

|

| ||||

| M08_RXDV | I | Pulldown | Receive data valid. M08_RXDV indicates data on M08_RXD7±M08_RXD0 is valid. This signal is | |||||

| synchronous to M08_RCLK. | ||||||||

|

|

|

|

| |||||

|

|

|

|

| |||||

| M08_RXER | I | Pulldown | Receive error. M08_RXER indicates reception of a coding error on received data. | |||||

|

|

|

|

|

|

|

|

| |

| M08_TXD7 |

|

|

|

|

|

|

| |

| M08_TXD6 |

|

|

|

|

|

|

| |

| M08_TXD5 |

|

| Transmit data. Byte transmit data. When M08_TXEN is asserted, these signals carry transmit data. | |||||

| M08_TXD4 | O | None | ||||||

| M08_TXD3 | Data on these signals is synchronous to M08_GTCLK. | |||||||

|

|

| |||||||

| M08_TXD2 |

|

|

|

|

|

|

| |

| M08_TXD1 |

|

|

|

|

|

|

| |

| M08_TXD0 |

|

|

|

|

|

|

| |

|

|

|

|

|

| ||||

| M08_TXEN | O | None | Transmit enable. M08_TXEN indicates valid transmit data on M08_TXD7±M08_TXD0. This signal | |||||

| is synchronous to M08_GTCLK. | ||||||||

|

|

|

|

| |||||

|

|

|

|

|

| ||||

|

|

|

|

| Transmit error. M08_TXER allows coding errors to be propagated between the | ||||

| M08_TXER | O | None | control (MAC) and the attached PHY. It is asserted at the end of an | |||||

|

|

|

|

| the device to force a coding error. | ||||

|

|

|

|

|

|

|

|

|

|

²Internal resistors are provided to pull signals to known values. The system designers should determine if additional pullups or pulldowns are required in their systems.

8 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |