TNETX4090

ThunderSWITCH II 9-PORT 100-/1000-MBIT/S ETHERNET SWITCH

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

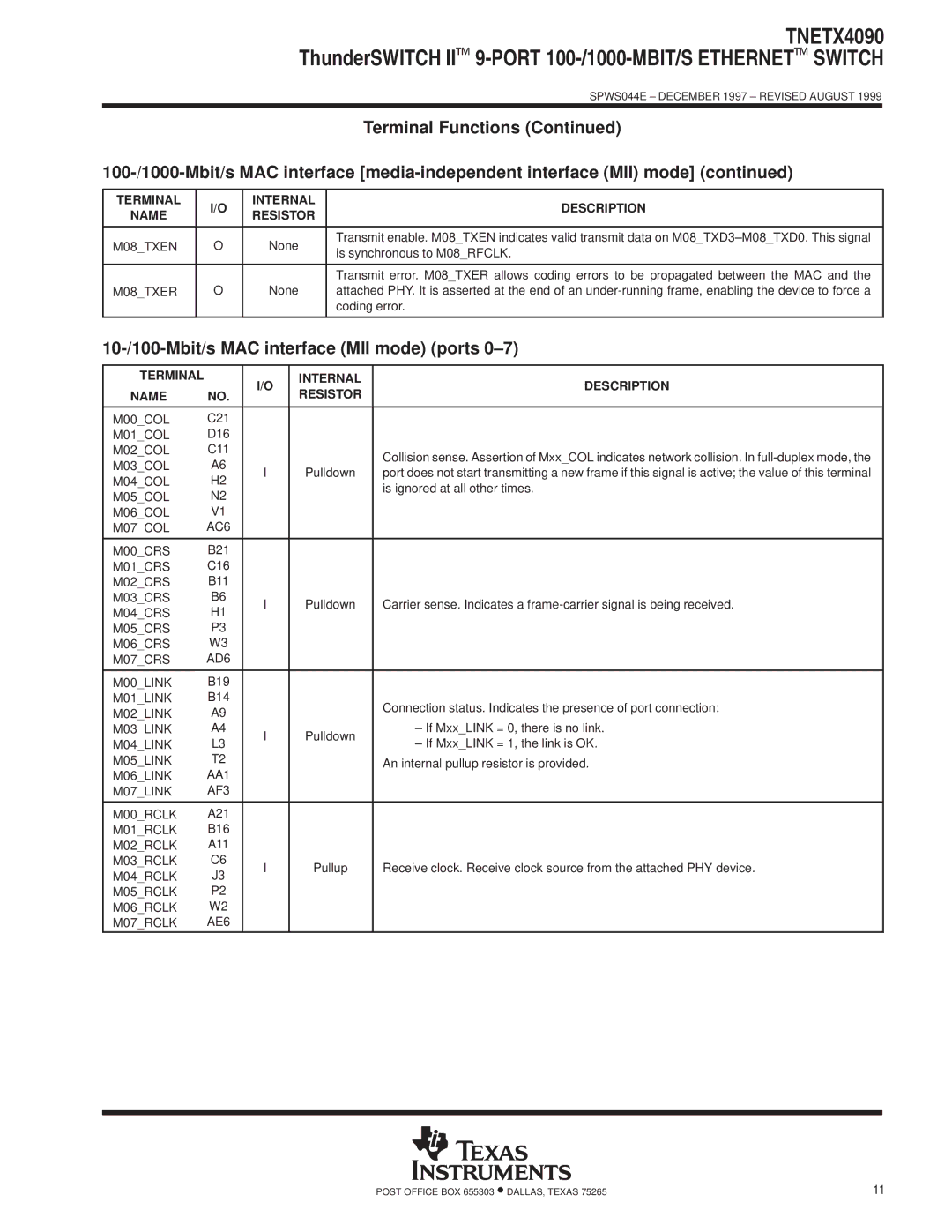

Terminal Functions (Continued)

TERMINAL | I/O | INTERNAL | DESCRIPTION | |

NAME | RESISTOR | |||

|

| |||

|

|

|

| |

M08_TXEN | O | None | Transmit enable. M08_TXEN indicates valid transmit data on M08_TXD3±M08_TXD0. This signal | |

is synchronous to M08_RFCLK. | ||||

|

|

| ||

|

|

|

| |

|

|

| Transmit error. M08_TXER allows coding errors to be propagated between the MAC and the | |

M08_TXER | O | None | attached PHY. It is asserted at the end of an | |

|

|

| coding error. | |

|

|

|

|

10-/100-Mbit/s MAC interface (MII mode) (ports 0±7)

TERMINAL |

| I/O | INTERNAL | DESCRIPTION | |

NAME | NO. | RESISTOR | |||

|

| ||||

|

|

|

|

| |

M00_COL | C21 |

|

|

| |

M01_COL | D16 |

|

|

| |

M02_COL | C11 |

|

| Collision sense. Assertion of Mxx_COL indicates network collision. In | |

M03_COL | A6 |

|

| ||

I | Pulldown | port does not start transmitting a new frame if this signal is active; the value of this terminal | |||

M04_COL | H2 | ||||

|

| is ignored at all other times. | |||

M05_COL | N2 |

|

| ||

|

|

| |||

M06_COL | V1 |

|

|

| |

M07_COL | AC6 |

|

|

| |

|

|

|

|

| |

M00_CRS | B21 |

|

|

| |

M01_CRS | C16 |

|

|

| |

M02_CRS | B11 |

|

|

| |

M03_CRS | B6 | I | Pulldown | Carrier sense. Indicates a | |

M04_CRS | H1 | ||||

|

|

| |||

M05_CRS | P3 |

|

|

| |

M06_CRS | W3 |

|

|

| |

M07_CRS | AD6 |

|

|

| |

|

|

|

|

| |

M00_LINK | B19 |

|

|

| |

M01_LINK | B14 |

|

| Connection status. Indicates the presence of port connection: | |

M02_LINK | A9 |

|

| ||

|

| ± If Mxx_LINK = 0, there is no link. | |||

M03_LINK | A4 | I | Pulldown | ||

M04_LINK | L3 | ± If Mxx_LINK = 1, the link is OK. | |||

|

| ||||

M05_LINK | T2 |

|

| An internal pullup resistor is provided. | |

M06_LINK | AA1 |

|

|

| |

M07_LINK | AF3 |

|

|

| |

|

|

|

|

| |

M00_RCLK | A21 |

|

|

| |

M01_RCLK | B16 |

|

|

| |

M02_RCLK | A11 |

|

|

| |

M03_RCLK | C6 | I | Pullup | Receive clock. Receive clock source from the attached PHY device. | |

M04_RCLK | J3 | ||||

|

|

| |||

M05_RCLK | P2 |

|

|

| |

M06_RCLK | W2 |

|

|

| |

M07_RCLK | AE6 |

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 11 |