|

|

|

|

| TNETX4090 | |

|

|

| ThunderSWITCH II | |||

|

|

|

|

| SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999 | |

|

|

|

|

|

|

|

|

|

|

| Terminal Functions (Continued) | ||

| ||||||

|

|

|

|

|

|

|

TERMINAL |

| I/O | INTERNAL |

| DESCRIPTION |

|

NAME | NO. | RESISTOR |

|

| ||

|

|

|

| |||

|

|

|

|

|

|

|

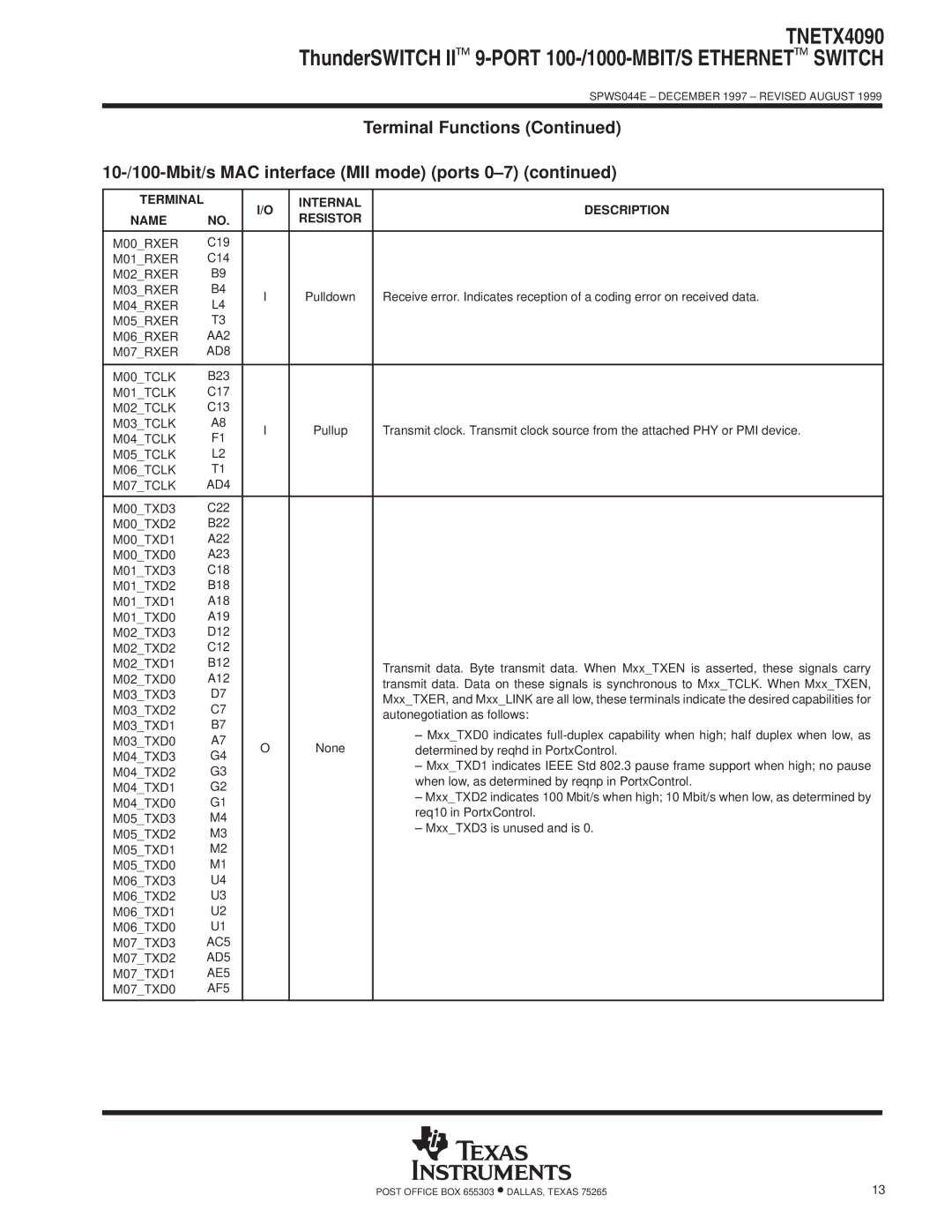

M00_RXER | C19 |

|

|

|

|

|

M01_RXER | C14 |

|

|

|

|

|

M02_RXER | B9 |

|

|

|

|

|

M03_RXER | B4 | I | Pulldown |

| Receive error. Indicates reception of a coding error on received data. |

|

M04_RXER | L4 |

|

| |||

|

|

|

|

| ||

M05_RXER | T3 |

|

|

|

|

|

M06_RXER | AA2 |

|

|

|

|

|

M07_RXER | AD8 |

|

|

|

|

|

|

|

|

|

|

|

|

M00_TCLK | B23 |

|

|

|

|

|

M01_TCLK | C17 |

|

|

|

|

|

M02_TCLK | C13 |

|

|

|

|

|

M03_TCLK | A8 | I | Pullup |

| Transmit clock. Transmit clock source from the attached PHY or PMI device. |

|

M04_TCLK | F1 |

|

| |||

|

|

|

|

| ||

M05_TCLK | L2 |

|

|

|

|

|

M06_TCLK | T1 |

|

|

|

|

|

M07_TCLK | AD4 |

|

|

|

|

|

|

|

|

|

|

|

|

M00_TXD3 | C22 |

|

|

|

|

|

M00_TXD2 | B22 |

|

|

|

|

|

M00_TXD1 | A22 |

|

|

|

|

|

M00_TXD0 | A23 |

|

|

|

|

|

M01_TXD3 | C18 |

|

|

|

|

|

M01_TXD2 | B18 |

|

|

|

|

|

M01_TXD1 | A18 |

|

|

|

|

|

M01_TXD0 | A19 |

|

|

|

|

|

M02_TXD3 | D12 |

|

|

|

|

|

M02_TXD2 | C12 |

|

|

|

|

|

M02_TXD1 | B12 |

|

|

| Transmit data. Byte transmit data. When Mxx_TXEN is asserted, these signals carry |

|

M02_TXD0 | A12 |

|

|

|

| |

|

|

| transmit data. Data on these signals is synchronous to Mxx_TCLK. When Mxx_TXEN, |

| ||

M03_TXD3 | D7 |

|

|

|

| |

|

|

| Mxx_TXER, and Mxx_LINK are all low, these terminals indicate the desired capabilities for |

| ||

M03_TXD2 | C7 |

|

|

|

| |

|

|

| autonegotiation as follows: |

| ||

M03_TXD1 | B7 |

|

|

|

| |

|

|

| ± Mxx_TXD0 indicates |

| ||

M03_TXD0 | A7 | O | None |

|

| |

| determined by reqhd in PortxControl. |

| ||||

M04_TXD3 | G4 |

|

| |||

|

|

| ± Mxx_TXD1 indicates IEEE Std 802.3 pause frame support when high; no pause |

| ||

M04_TXD2 | G3 |

|

|

|

| |

|

|

| when low, as determined by reqnp in PortxControl. |

| ||

M04_TXD1 | G2 |

|

|

|

| |

|

|

| ± Mxx_TXD2 indicates 100 Mbit/s when high; 10 Mbit/s when low, as determined by |

| ||

M04_TXD0 | G1 |

|

|

|

| |

|

|

| req10 in PortxControl. |

| ||

M05_TXD3 | M4 |

|

|

|

| |

|

|

| ± Mxx_TXD3 is unused and is 0. |

| ||

M05_TXD2 | M3 |

|

|

|

| |

|

|

|

|

| ||

M05_TXD1 | M2 |

|

|

|

|

|

M05_TXD0 | M1 |

|

|

|

|

|

M06_TXD3 | U4 |

|

|

|

|

|

M06_TXD2 | U3 |

|

|

|

|

|

M06_TXD1 | U2 |

|

|

|

|

|

M06_TXD0 | U1 |

|

|

|

|

|

M07_TXD3 | AC5 |

|

|

|

|

|

M07_TXD2 | AD5 |

|

|

|

|

|

M07_TXD1 | AE5 |

|

|

|

|

|

M07_TXD0 | AF5 |

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 13 |