TNETX4090

ThunderSWITCH II 9-PORT 100-/1000-MBIT/S ETHERNET SWITCH

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

|

| Table 12. Directed Format Receive Pretag Bit Definitions | |

|

|

| |

BIT | NAME | FUNCTION | |

|

|

| |

|

| One. Indicates directed format. The frame is routed to port(s) specified in portvector that are enabled (disabled in | |

|

| portxcontrol = 0), regardless of whether the destination address is unicast or multicast (i.e., the destination address | |

|

| is not examined). | |

31 | 1 | The internal | |

|

| RxUniBlockPorts, and RxMultiBlockPorts registers also have no effect on frame reception or transmission. | |

|

| Portvector is not examined to see if the source port has been specified as a destination port, so it is possible to send | |

|

| a frame back out of port 8. If portvector is 0, the frame is discarded. | |

|

|

| |

30±10 | reserved | Reserved. Bits 30±10 are ignored. | |

|

|

| |

9±0 | portvector | Destination port vector. A bit for each port on this device. A 1 in position n indicates the frame is destined for port n | |

on this device. | |||

|

| ||

|

|

|

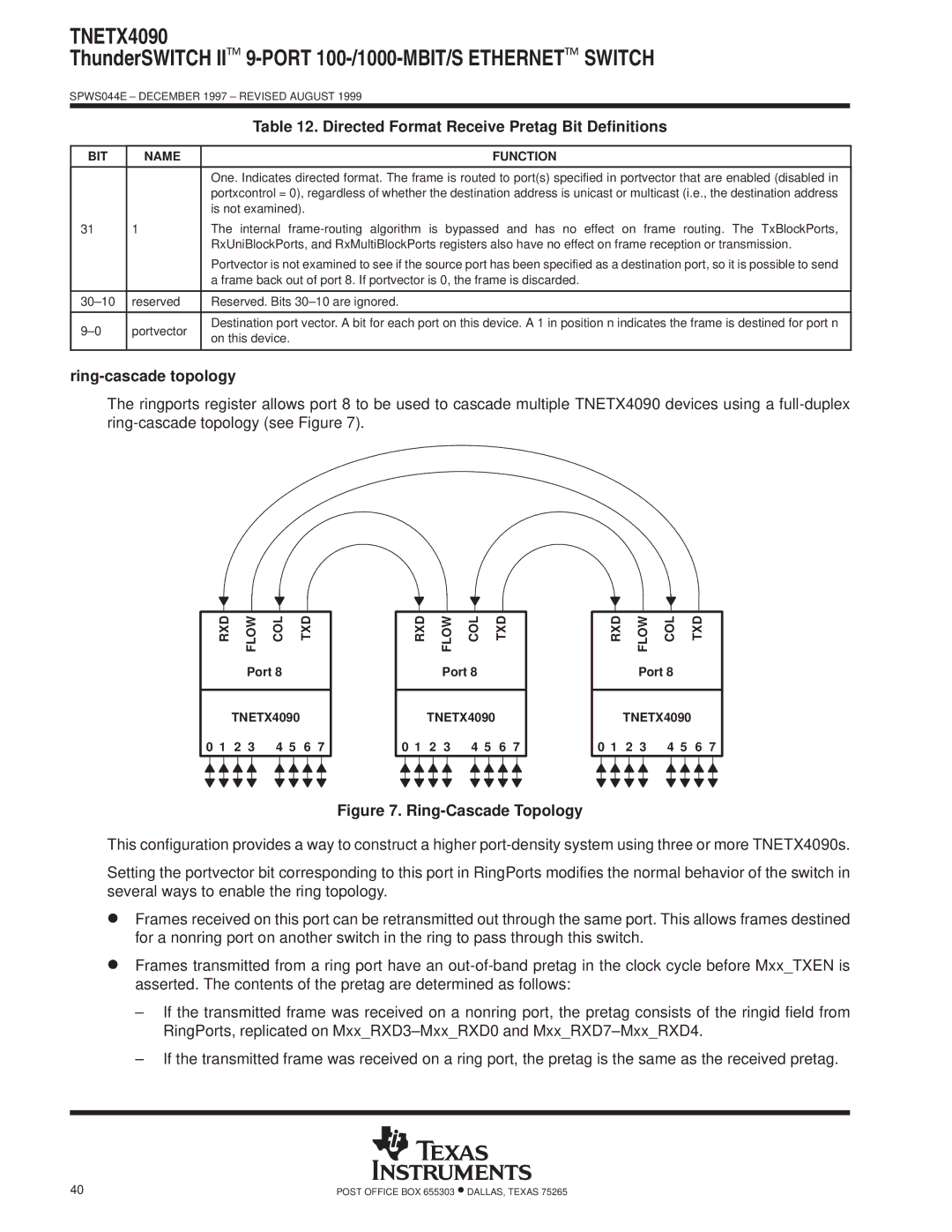

ring-cascade topology

The ringports register allows port 8 to be used to cascade multiple TNETX4090 devices using a

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RXD |

|

| FLOW | COL | TXD |

|

| |||||

|

|

|

|

| Port 8 |

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| TNETX4090 |

|

|

|

| ||||||

0 1 | 2 | 3 | 4 5 | 6 | 7 | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RXD |

|

| FLOW | COL | TXD |

|

| |||||

|

|

|

|

| Port 8 |

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| TNETX4090 |

|

|

|

| ||||||

0 1 | 2 | 3 | 4 5 | 6 | 7 | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| RXD |

|

| FLOW | COL | TXD |

|

| |||||

|

|

|

|

| Port 8 |

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

| TNETX4090 |

|

|

|

| ||||||

0 1 | 2 | 3 | 4 5 | 6 | 7 | ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 7. Ring-Cascade Topology

This configuration provides a way to construct a higher

Setting the portvector bit corresponding to this port in RingPorts modifies the normal behavior of the switch in several ways to enable the ring topology.

DFrames received on this port can be retransmitted out through the same port. This allows frames destined for a nonring port on another switch in the ring to pass through this switch.

DFrames transmitted from a ring port have an

±If the transmitted frame was received on a nonring port, the pretag consists of the ringid field from RingPorts, replicated on Mxx_RXD3±Mxx_RXD0 and Mxx_RXD7±Mxx_RXD4.

±If the transmitted frame was received on a ring port, the pretag is the same as the received pretag.

40 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |