TNETX4090 ThunderSWITCH II

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

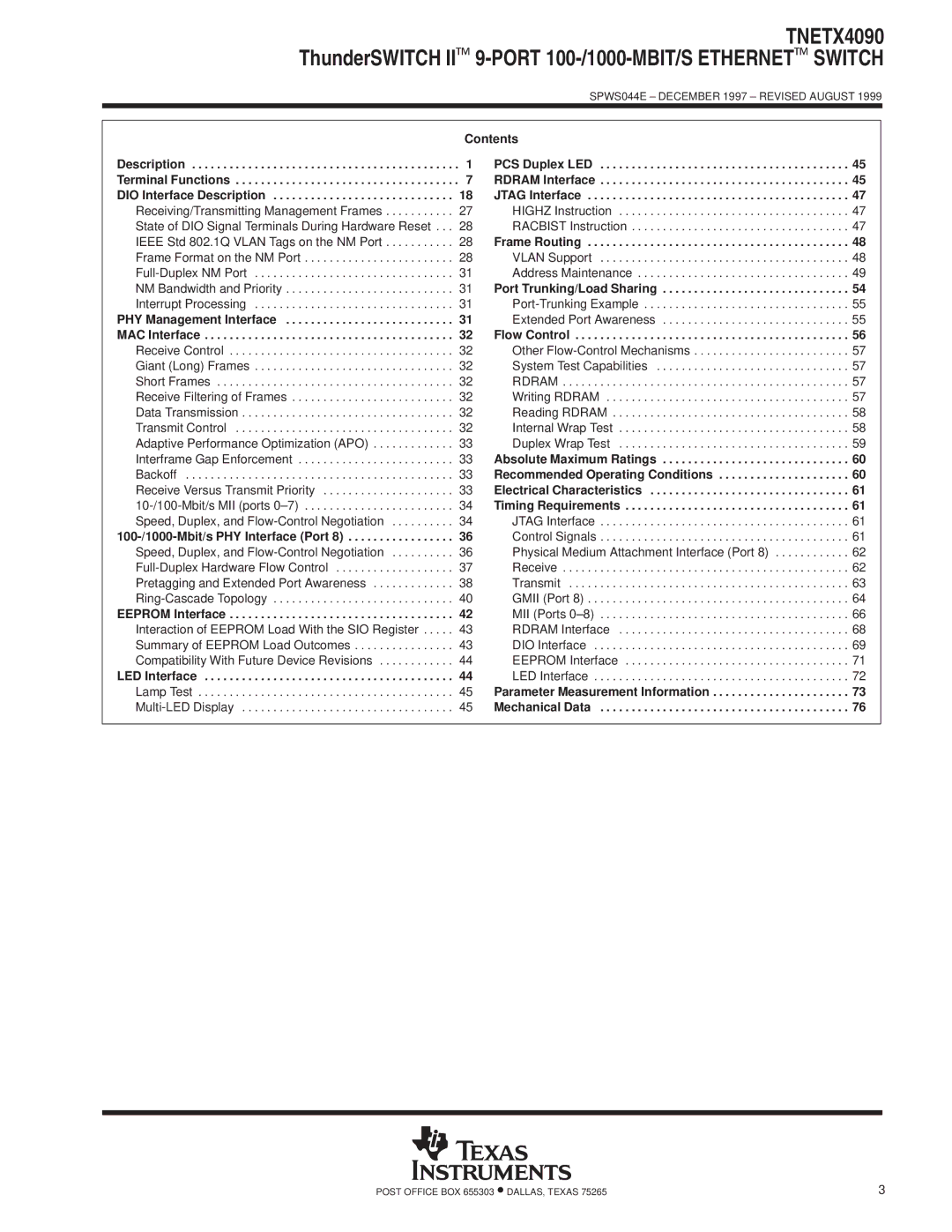

Contents

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Terminal Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

DIO Interface Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Receiving/Transmitting Management Frames . . . . . . . . . . . 27 State of DIO Signal Terminals During Hardware Reset . . . 28 IEEE Std 802.1Q VLAN Tags on the NM Port . . . . . . . . . . . 28 Frame Format on the NM Port . . . . . . . . . . . . . . . . . . . . . . . . 28

PHY Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 MAC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Receive Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Giant (Long) Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Short Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Receive Filtering of Frames . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Data Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Transmit Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Adaptive Performance Optimization (APO) . . . . . . . . . . . . . 33

Interframe Gap Enforcement . . . . . . . . . . . . . . . . . . . . . . . . . 33

Backoff . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Receive Versus Transmit Priority . . . . . . . . . . . . . . . . . . . . . 33

Speed, Duplex, and

100-/1000-Mbit/s PHY Interface (Port 8) . . . . . . . . . . . . . . . . . 36

Speed, Duplex, and

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Interaction of EEPROM Load With the SIO Register . . . . . 43 Summary of EEPROM Load Outcomes . . . . . . . . . . . . . . . . 43 Compatibility With Future Device Revisions . . . . . . . . . . . . 44

LED Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Lamp Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

PCS Duplex LED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

RDRAM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

HIGHZ Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 RACBIST Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Frame Routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

VLAN Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Address Maintenance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Port Trunking/Load Sharing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Other

System Test Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

RDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Writing RDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Reading RDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Internal Wrap Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Duplex Wrap Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . 60

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Physical Medium Attachment Interface (Port 8) . . . . . . . . . . . . 62

Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

GMII (Port 8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

MII (Ports 0±8) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

RDRAM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

DIO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

LED Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Parameter Measurement Information . . . . . . . . . . . . . . . . . . . . . . 73 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 3 |