TNETX4090

ThunderSWITCH II 9-PORT 100-/1000-MBIT/S ETHERNET SWITCH

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

ring-cascade topology (continued)

DFrames received on a ring port must have an

±The pretag is 0.

±The two IDs within the pretag are not the same.

±The ID within the received pretag is the same as ringid. This identifies a frame that originated at this device, and that has passed completely around the ring.

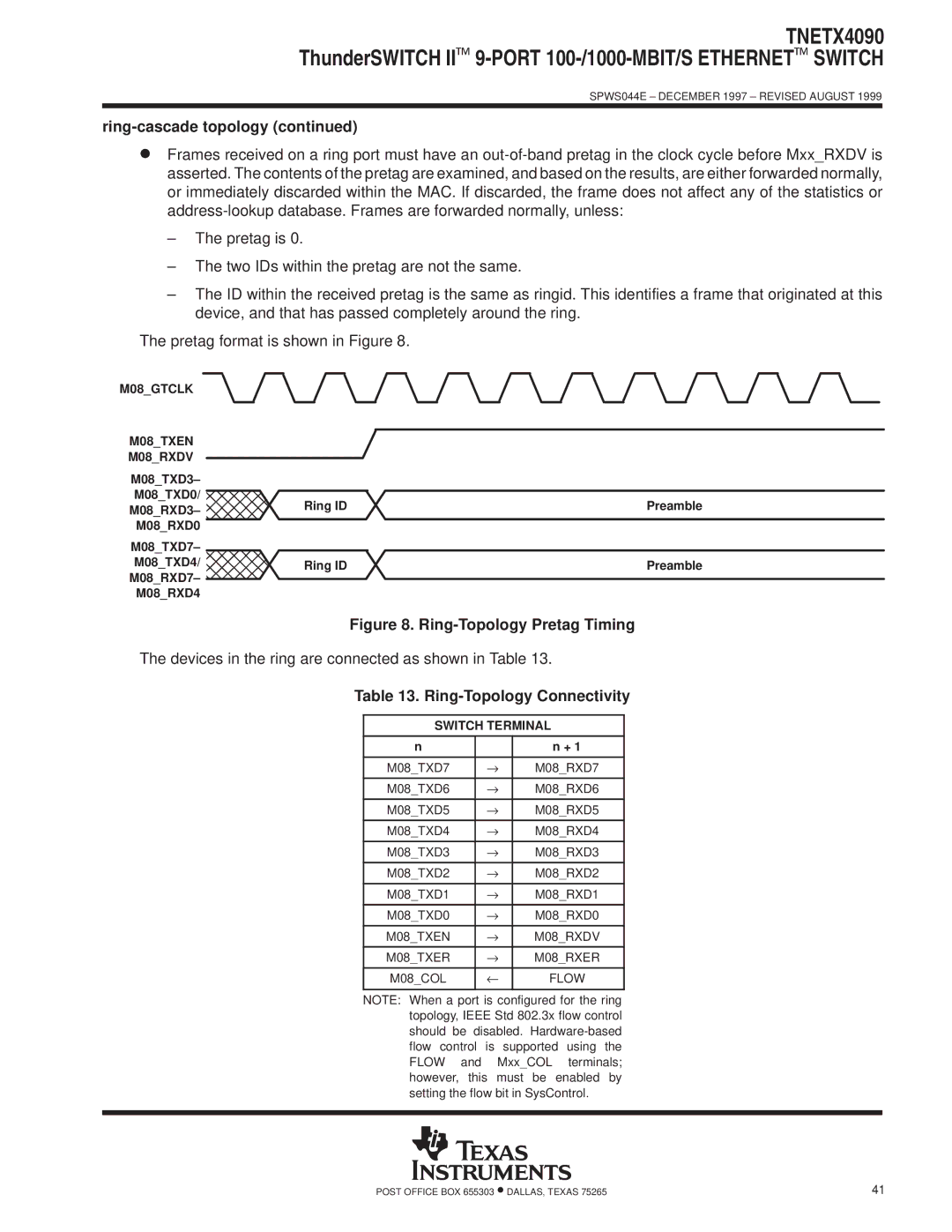

The pretag format is shown in Figure 8.

M08_GTCLK

M08_TXEN

M08_RXDV

M08_TXD3± |

|

| |

M08_TXD0/ | Ring ID | Preamble | |

M08_RXD3± | |||

|

| ||

M08_RXD0 |

|

| |

M08_TXD7± |

|

| |

M08_TXD4/ | Ring ID | Preamble | |

M08_RXD7± |

|

| |

M08_RXD4 |

|

|

Figure 8. Ring-Topology Pretag Timing

The devices in the ring are connected as shown in Table 13.

Table 13. Ring-Topology Connectivity

SWITCH TERMINAL

n |

| n + 1 |

|

|

|

M08_TXD7 | → | M08_RXD7 |

|

|

|

M08_TXD6 | → | M08_RXD6 |

|

|

|

M08_TXD5 | → | M08_RXD5 |

|

|

|

M08_TXD4 | → | M08_RXD4 |

|

|

|

M08_TXD3 | → | M08_RXD3 |

|

|

|

M08_TXD2 | → | M08_RXD2 |

|

|

|

M08_TXD1 | → | M08_RXD1 |

|

|

|

M08_TXD0 | → | M08_RXD0 |

|

|

|

M08_TXEN | → | M08_RXDV |

|

|

|

M08_TXER | → | M08_RXER |

|

|

|

M08_COL | ← | FLOW |

|

|

|

NOTE: When a port is configured for the ring topology, IEEE Std 802.3x flow control should be disabled.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 41 |