TNETX4090

ThunderSWITCH II 9-PORT 100-/1000-MBIT/S ETHERNET SWITCH

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

|

|

|

|

|

|

|

|

|

|

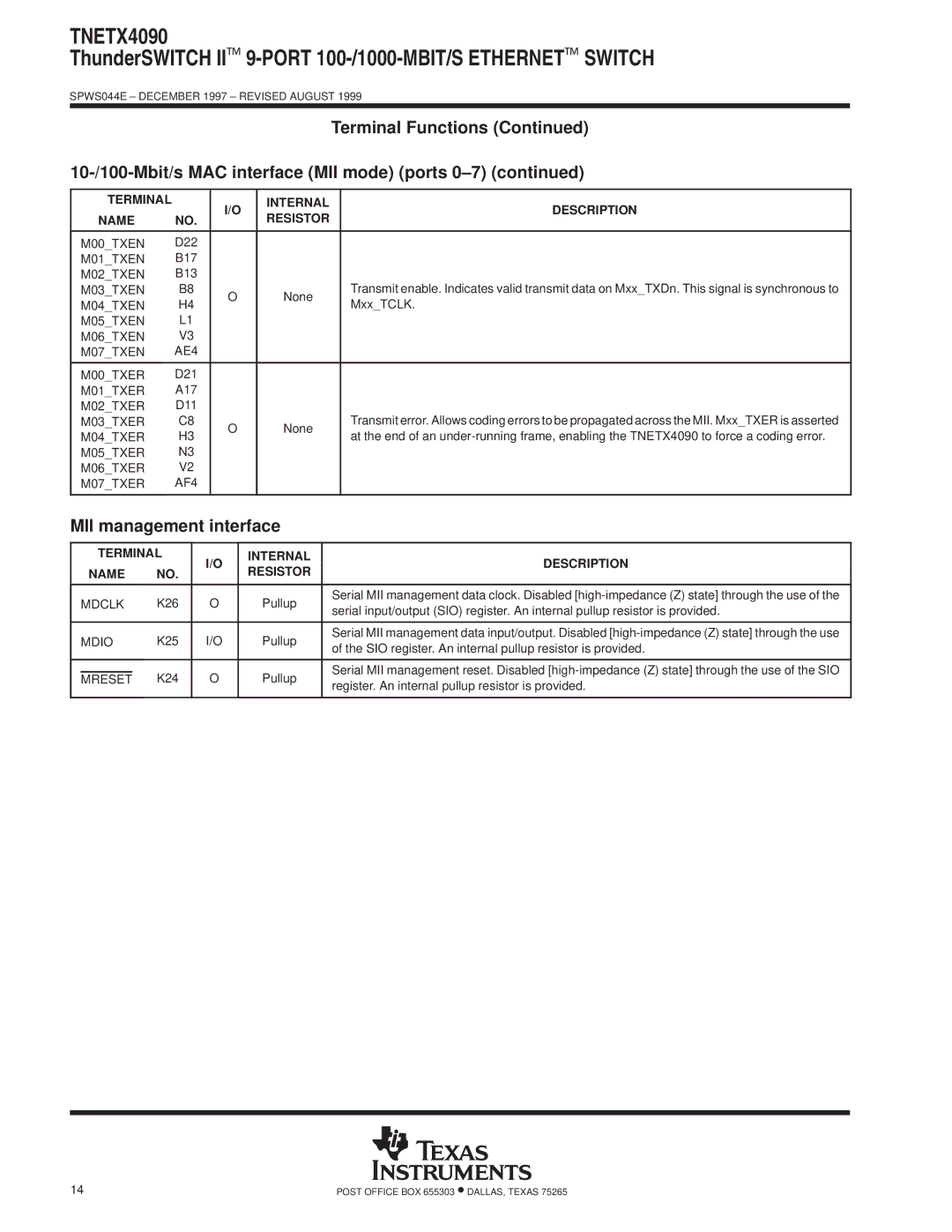

| Terminal Functions (Continued) | |

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

| TERMINAL |

| I/O |

| INTERNAL |

| DESCRIPTION | |||||

| NAME | NO. |

|

| RESISTOR |

| ||||||

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| M00_TXEN | D22 |

|

|

|

|

|

|

|

| ||

| M01_TXEN | B17 |

|

|

|

|

|

|

|

| ||

| M02_TXEN | B13 |

|

|

|

|

|

|

| Transmit enable. Indicates valid transmit data on Mxx_TXDn. This signal is synchronous to | ||

| M03_TXEN | B8 |

| O |

| None |

| |||||

| M04_TXEN | H4 |

|

|

| Mxx_TCLK. | ||||||

|

|

|

|

|

|

|

| |||||

| M05_TXEN | L1 |

|

|

|

|

|

|

|

| ||

| M06_TXEN | V3 |

|

|

|

|

|

|

|

| ||

| M07_TXEN | AE4 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| M00_TXER | D21 |

|

|

|

|

|

|

|

| ||

| M01_TXER | A17 |

|

|

|

|

|

|

|

| ||

| M02_TXER | D11 |

|

|

|

|

|

|

| Transmit error. Allows coding errors to be propagated across the MII. Mxx_TXER is asserted | ||

| M03_TXER | C8 |

| O |

| None |

| |||||

| M04_TXER | H3 |

|

|

| at the end of an | ||||||

|

|

|

|

|

|

|

| |||||

| M05_TXER | N3 |

|

|

|

|

|

|

|

| ||

| M06_TXER | V2 |

|

|

|

|

|

|

|

| ||

| M07_TXER | AF4 |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

| |||

MII management interface |

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

| ||

| TERMINAL |

| I/O |

| INTERNAL |

|

| DESCRIPTION | ||||

| NAME | NO. |

|

| RESISTOR |

|

| |||||

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

| |

| MDCLK | K26 |

| O |

|

| Pullup |

| Serial MII management data clock. Disabled | |||

|

|

|

|

| serial input/output (SIO) register. An internal pullup resistor is provided. | |||||||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

| MDIO | K25 |

| I/O |

|

| Pullup |

| Serial MII management data input/output. Disabled | |||

|

|

|

|

| of the SIO register. An internal pullup resistor is provided. | |||||||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| K24 |

| O |

|

| Pullup |

| Serial MII management reset. Disabled | ||

| MRESET |

|

|

|

| |||||||

|

|

|

|

| register. An internal pullup resistor is provided. | |||||||

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

14 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |