|

| TNETX4090 | |

|

| ThunderSWITCH II | |

|

| SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999 | |

|

|

|

|

|

| Table 10. Transmit Pretag Bit Definitions | |

|

|

|

|

BIT | NAME | FUNCTION |

|

|

|

|

|

31±28 | reserved | Reserved. These bits always are 0. |

|

|

|

|

|

|

| Receive header. Indicates whether an IEEE Std 802.1Q header was added to the frame on reception. |

|

27 | rxheader | ± When rxheader = 1, an IEEE Std 802.1Q header was inserted. |

|

|

| ± When rxheader = 0, no IEEE Std 802.1Q header was inserted. |

|

|

|

|

|

26±25 | reserved | Reserved. These bits always are 0. |

|

|

|

|

|

24±20 | portcode | Source port code. Indicates which port on the device received the frame. Codes 00000±01001 indicate ports 0±9, |

|

respectively (port 9 is the NM DIO port). All other codes are reserved and are not generated. |

| ||

|

|

| |

|

|

|

|

19±17 | reserved | Reserved. These bits always are 0. |

|

|

|

|

|

16±0 | xportvector² | Extended destination port vector. A bit for each port on the crossbar matrix. A 1 in position n indicates the frame is |

|

destined for port n on the crossbar matrix. |

| ||

|

|

| |

|

|

|

|

²Bit vector, in which bit x corresponds to external crossbar matrix port x. Any number of ports can be selected at the same time.

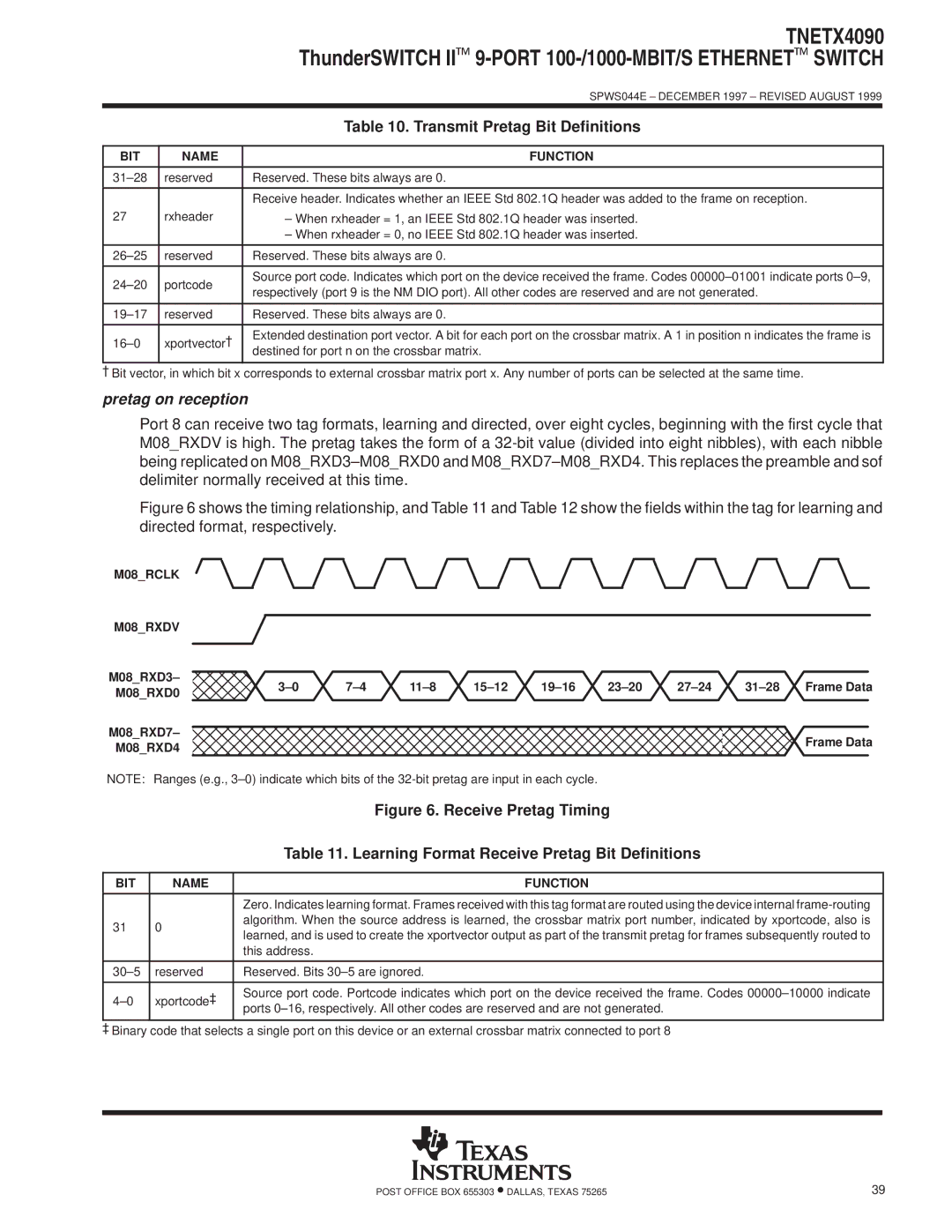

pretag on reception

Port 8 can receive two tag formats, learning and directed, over eight cycles, beginning with the first cycle that M08_RXDV is high. The pretag takes the form of a

Figure 6 shows the timing relationship, and Table 11 and Table 12 show the fields within the tag for learning and directed format, respectively.

M08_RCLK

M08_RXDV

M08_RXD3± | 3±0 | 7±4 | 11±8 | 15±12 | 19±16 | 23±20 | 27±24 | 31±28 | Frame Data | |

M08_RXD0 | ||||||||||

|

|

|

|

|

|

|

|

|

M08_RXD7± |

|

|

|

|

|

| Frame Data | ||

M08_RXD4 |

|

| ||

|

|

|

| |

NOTE: Ranges (e.g., 3±0) indicate which bits of the

|

| Figure 6. Receive Pretag Timing | |

|

| Table 11. Learning Format Receive Pretag Bit Definitions | |

|

|

| |

BIT | NAME | FUNCTION | |

|

|

| |

|

| Zero. Indicates learning format. Frames received with this tag format are routed using the device internal | |

31 | 0 | algorithm. When the source address is learned, the crossbar matrix port number, indicated by xportcode, also is | |

learned, and is used to create the xportvector output as part of the transmit pretag for frames subsequently routed to | |||

|

| ||

|

| this address. | |

|

|

| |

30±5 | reserved | Reserved. Bits 30±5 are ignored. | |

|

|

| |

4±0 | xportcode³ | Source port code. Portcode indicates which port on the device received the frame. Codes 00000±10000 indicate | |

ports 0±16, respectively. All other codes are reserved and are not generated. | |||

|

| ||

|

|

|

³Binary code that selects a single port on this device or an external crossbar matrix connected to port 8

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 39 |