|

|

|

|

|

|

| TNETX4090 | |

|

|

|

| ThunderSWITCH II | ||||

|

|

|

|

|

|

| SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999 | |

|

|

|

|

|

|

|

|

|

|

|

|

|

| Terminal Functions (Continued) | |||

|

|

|

|

|

|

|

|

|

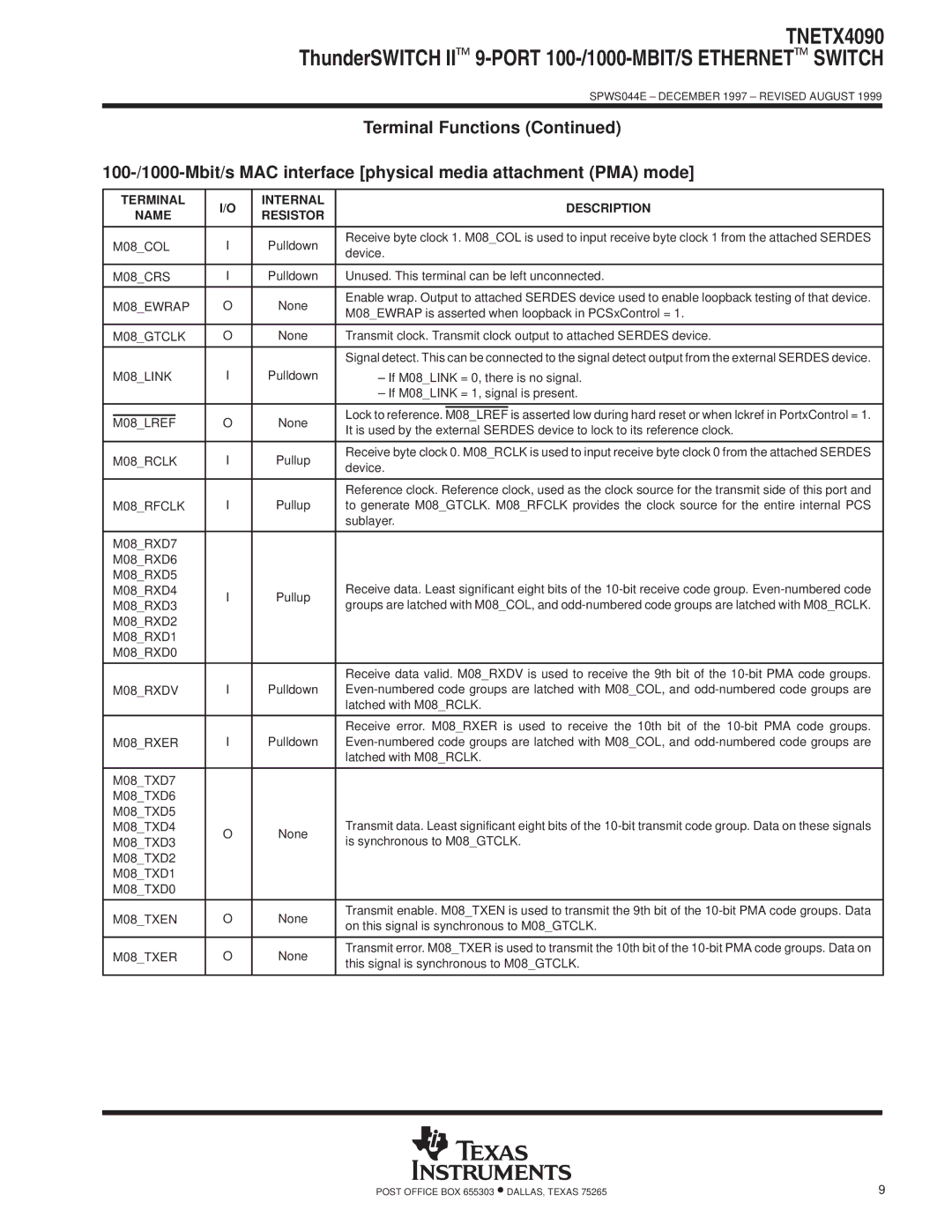

| TERMINAL | I/O | INTERNAL |

|

| DESCRIPTION |

| |

| NAME | RESISTOR |

|

|

| |||

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| M08_COL | I | Pulldown | Receive byte clock 1. M08_COL is used to input receive byte clock 1 from the attached SERDES |

| |||

| device. |

| ||||||

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| M08_CRS | I | Pulldown | Unused. This terminal can be left unconnected. |

| |||

|

|

|

|

|

|

|

|

|

| M08_EWRAP | O | None | Enable wrap. Output to attached SERDES device used to enable loopback testing of that device. |

| |||

| M08_EWRAP is asserted when loopback in PCSxControl = 1. |

| ||||||

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| M08_GTCLK | O | None | Transmit clock. Transmit clock output to attached SERDES device. |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Signal detect. This can be connected to the signal detect output from the external SERDES device. |

| ||

| M08_LINK | I | Pulldown | ± If M08_LINK = 0, there is no signal. |

| |||

|

|

|

|

| ± If M08_LINK = 1, signal is present. |

| ||

|

|

|

|

|

|

| ||

|

|

|

|

| Lock to reference. |

| is asserted low during hard reset or when lckref in PortxControl = 1. |

|

|

|

|

|

| M08_LREF |

| ||

| M08_LREF | O | None | |||||

| It is used by the external SERDES device to lock to its reference clock. |

| ||||||

|

|

|

|

|

| |||

|

|

|

|

|

|

| ||

| M08_RCLK | I | Pullup | Receive byte clock 0. M08_RCLK is used to input receive byte clock 0 from the attached SERDES |

| |||

| device. |

| ||||||

|

|

|

|

|

| |||

|

|

|

|

|

|

| ||

|

|

|

|

| Reference clock. Reference clock, used as the clock source for the transmit side of this port and |

| ||

| M08_RFCLK | I | Pullup | to generate M08_GTCLK. M08_RFCLK provides the clock source for the entire internal PCS |

| |||

|

|

|

|

| sublayer. |

| ||

|

|

|

|

|

|

|

| |

| M08_RXD7 |

|

|

|

|

|

| |

| M08_RXD6 |

|

|

|

|

|

| |

| M08_RXD5 |

|

| Receive data. Least significant eight bits of the |

| |||

| M08_RXD4 | I | Pullup |

| ||||

| M08_RXD3 | groups are latched with M08_COL, and |

| |||||

|

|

|

| |||||

| M08_RXD2 |

|

|

|

|

|

| |

| M08_RXD1 |

|

|

|

|

|

| |

| M08_RXD0 |

|

|

|

|

|

| |

|

|

|

|

|

|

| ||

|

|

|

|

| Receive data valid. M08_RXDV is used to receive the 9th bit of the |

| ||

| M08_RXDV | I | Pulldown |

| ||||

|

|

|

|

| latched with M08_RCLK. |

| ||

|

|

|

|

|

|

| ||

|

|

|

|

| Receive error. M08_RXER is used to receive the 10th bit of the |

| ||

| M08_RXER | I | Pulldown |

| ||||

|

|

|

|

| latched with M08_RCLK. |

| ||

|

|

|

|

|

|

|

| |

| M08_TXD7 |

|

|

|

|

|

| |

| M08_TXD6 |

|

|

|

|

|

| |

| M08_TXD5 |

|

| Transmit data. Least significant eight bits of the |

| |||

| M08_TXD4 | O | None |

| ||||

| M08_TXD3 | is synchronous to M08_GTCLK. |

| |||||

|

|

|

| |||||

| M08_TXD2 |

|

|

|

|

|

| |

| M08_TXD1 |

|

|

|

|

|

| |

| M08_TXD0 |

|

|

|

|

|

| |

|

|

|

|

|

|

| ||

| M08_TXEN | O | None | Transmit enable. M08_TXEN is used to transmit the 9th bit of the |

| |||

| on this signal is synchronous to M08_GTCLK. |

| ||||||

|

|

|

|

|

| |||

|

|

|

|

|

|

| ||

| M08_TXER | O | None | Transmit error. M08_TXER is used to transmit the 10th bit of the |

| |||

| this signal is synchronous to M08_GTCLK. |

| ||||||

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 | 9 |