TNETX4090

ThunderSWITCH II 9-PORT 100-/1000-MBIT/S ETHERNET SWITCH

SPWS044E ± DECEMBER 1997 ± REVISED AUGUST 1999

EEPROM interface

The EEPROM interface is provided so the

The EEPROM contains configuration and initialization information that is accessed infrequently, typically at power up and after a reset. The organization of the EEPROM data is shown in the DIO address map. Downloads are initiated in one of two ways:

DAt the end of hard reset (rising edge on RESET)

DWriting a 1 to load in SysControl register. This bit is cleared automatically when the download completes. It cannot be set during the download by the EEPROM data, thereby preventing a download loop.

During the download, no DIO writes are permitted. (If a DIO write is attempted, SRDY is held high until the download has completed.)

Either a 24C02 or 24C08 serial EEPROM device can be used. Both use a

DThe 24C02 provides 2048 bits, organized as 256 ⋅ 8. Downloading data from the EEPROM initializes DIO addresses 0x0000 through 0x00FB. These registers control all initializable functions except VLANs. The downloading sequence starts with DIO address 0x0000, continuing in ascending order to 0x00FF.

DThe 24C08 provides 8192 bits, organized as 1024 ⋅8. Downloading data from the EEPROM initializes DIO addresses 0x0000 through 0x03FF. These registers control all initializable functions, including VLANs. The downloading sequence starts with DIO address 0x0100, continuing in ascending order to 0x03FF, followed by address 0x0000, continuing in ascending order to 0x00FF. This ensures that SysControl is the last register loaded.

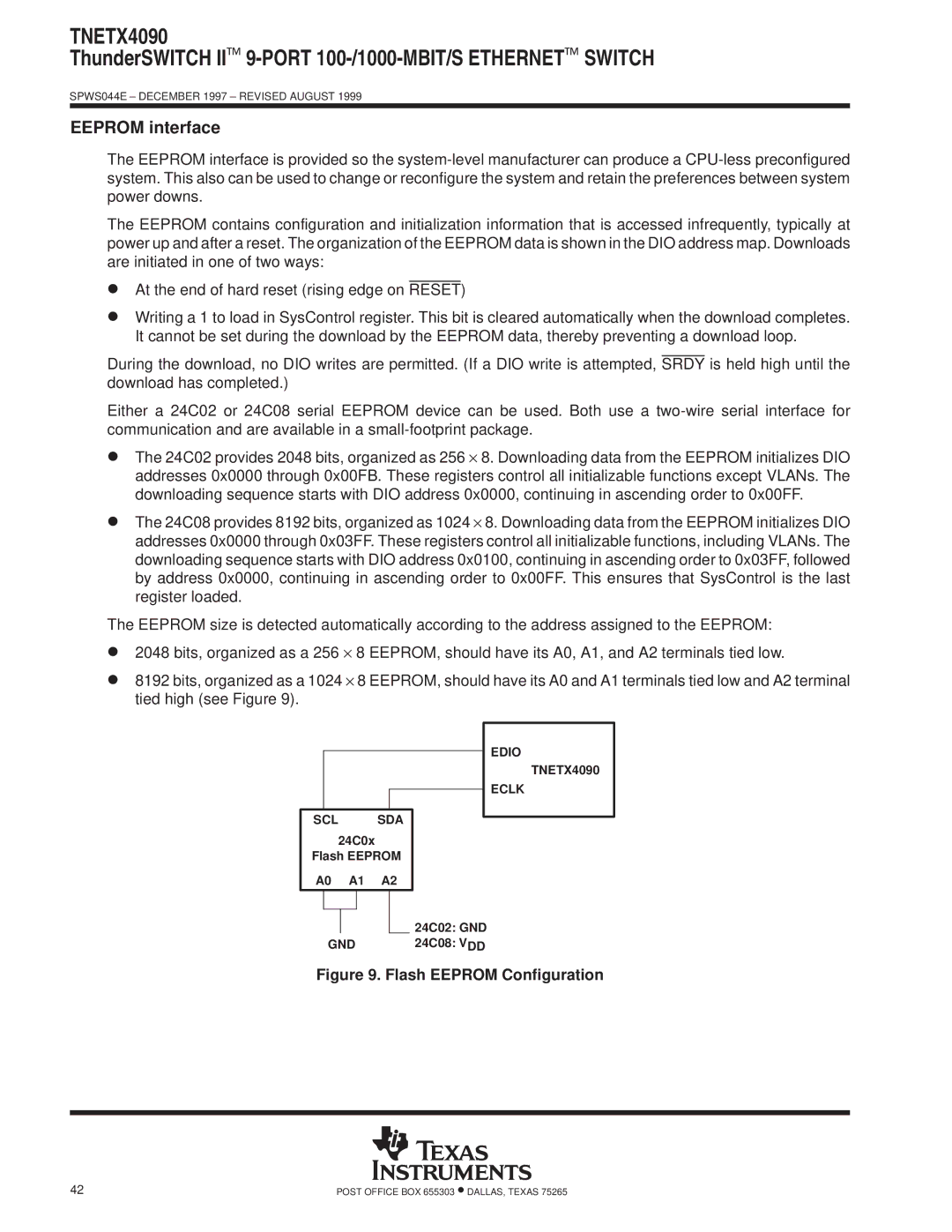

The EEPROM size is detected automatically according to the address assigned to the EEPROM:

D2048 bits, organized as a 256 ⋅ 8 EEPROM, should have its A0, A1, and A2 terminals tied low.

D8192 bits, organized as a 1024 ⋅8 EEPROM, should have its A0 and A1 terminals tied low and A2 terminal tied high (see Figure 9).

SCL SDA

24C0x

Flash EEPROM

EDIO

TNETX4090

ECLK

A0 A1 A2

|

|

|

|

|

| 24C02: GND |

|

|

|

|

|

| |

| GND |

|

| 24C08: VDD | ||

Figure 9. Flash EEPROM Configuration

42 | POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |