STATUS BYTE

Status data structure - register model

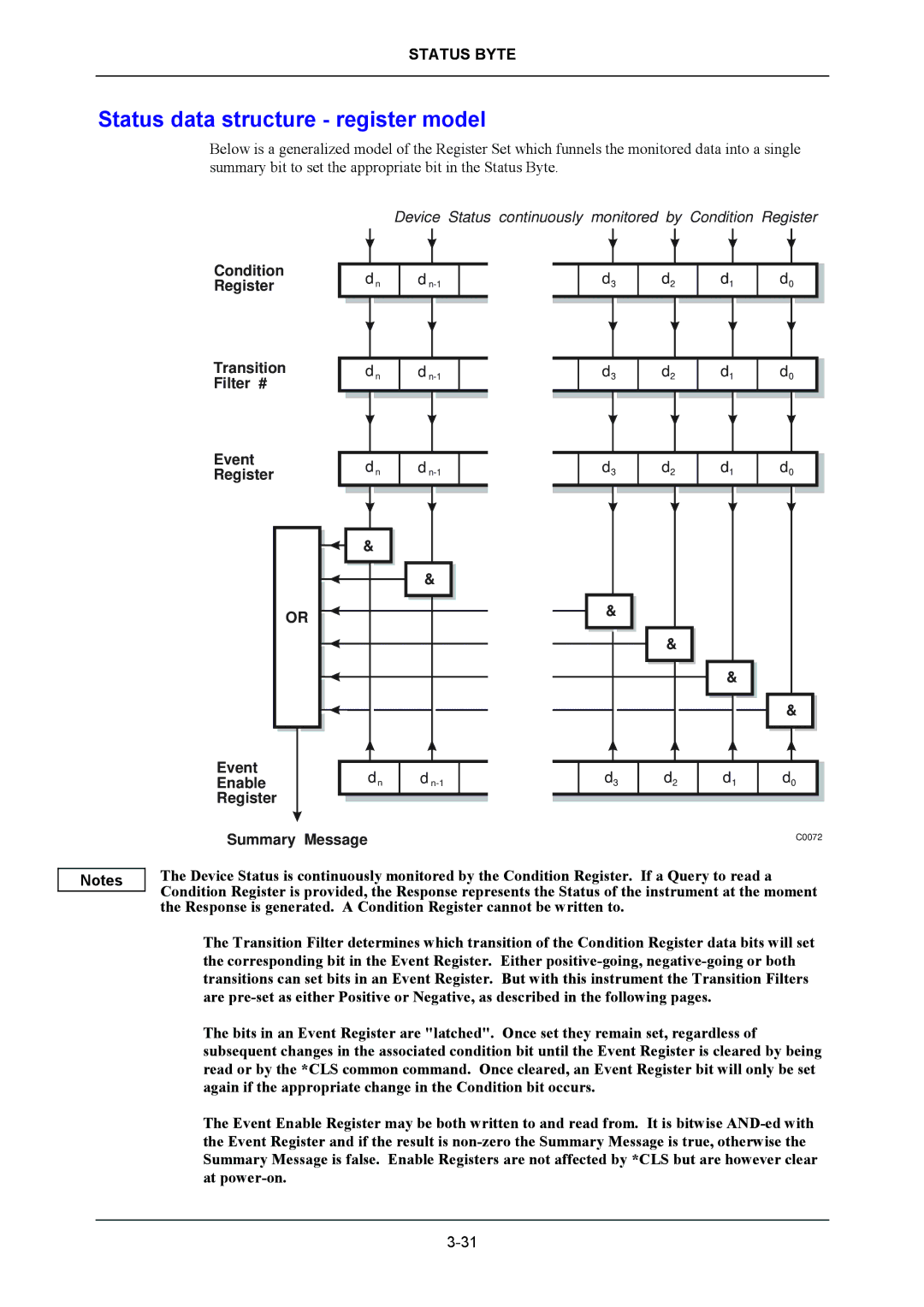

Below is a generalized model of the Register Set which funnels the monitored data into a single summary bit to set the appropriate bit in the Status Byte.

Device Status continuously monitored by Condition Register

Condition | dn | d |

Register |

Transition |

|

|

|

|

|

dn | d |

| |||

Filter # |

|

|

|

|

|

Event | dn | d |

|

Register |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| d3 | d2 | d1 | d0 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d3 | d2 | d1 | d0 |

|

|

|

|

|

|

|

|

|

| d3 | d2 | d1 | d0 | ||||

|

|

|

|

|

|

|

|

|

OR |

Event

Enable

Register

& |

& |

dn | d |

|

& |

& |

& |

& |

| d3 | d2 | d1 | d0 |

|

|

|

|

|

Summary Message

C0072

Notes

The Device Status is continuously monitored by the Condition Register. If a Query to read a Condition Register is provided, the Response represents the Status of the instrument at the moment the Response is generated. A Condition Register cannot be written to.

The Transition Filter determines which transition of the Condition Register data bits will set the corresponding bit in the Event Register. Either

The bits in an Event Register are "latched". Once set they remain set, regardless of subsequent changes in the associated condition bit until the Event Register is cleared by being read or by the *CLS common command. Once cleared, an Event Register bit will only be set again if the appropriate change in the Condition bit occurs.

The Event Enable Register may be both written to and read from. It is bitwise