STATUS BYTE

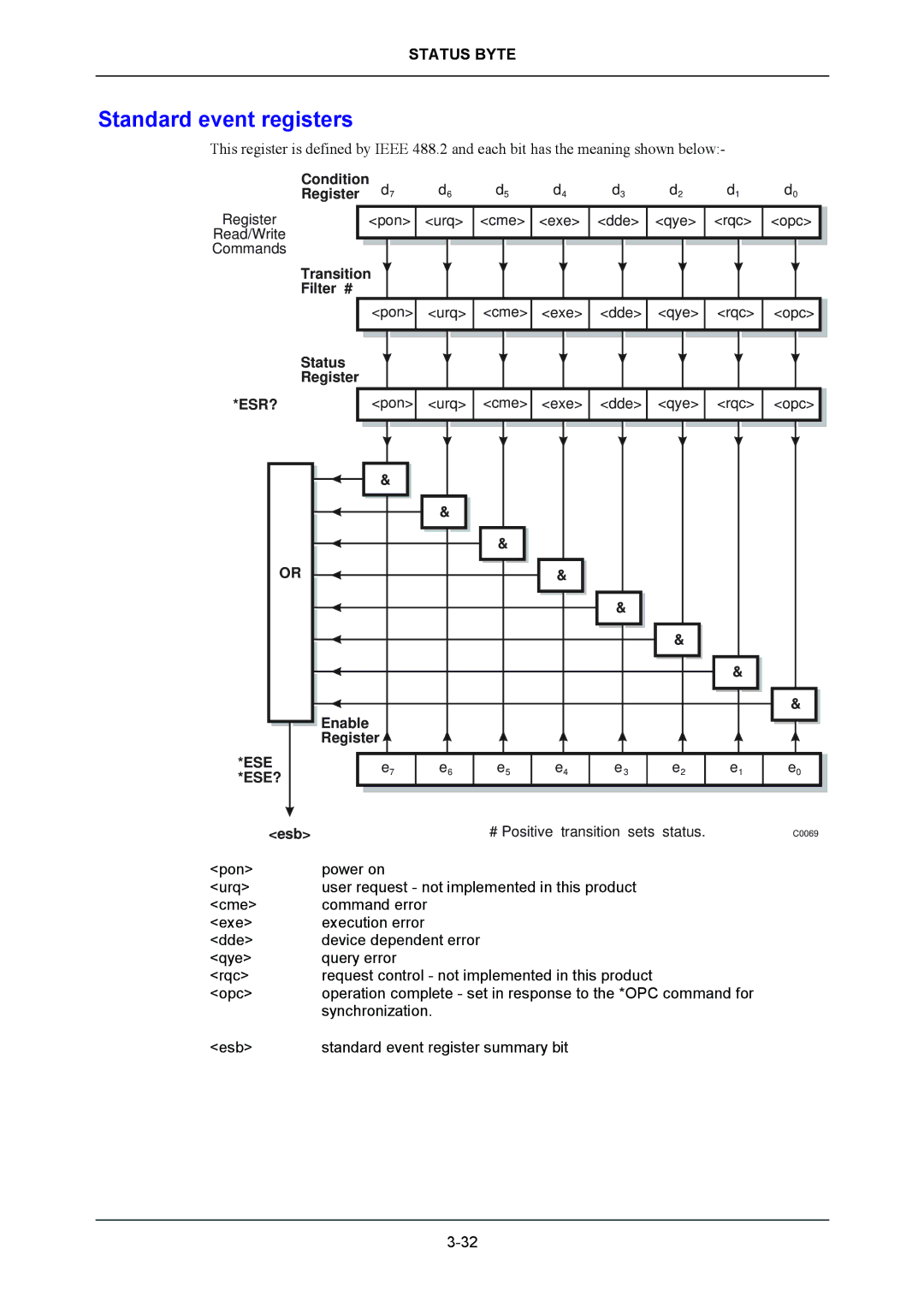

Standard event registers

This register is defined by IEEE 488.2 and each bit has the meaning shown below:-

Condition | d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 |

Register |

Register

Read/Write

Commands

<pon> <urq> <cme> <exe> <dde> <qye>

<rqc> <opc>

Transition Filter #

<pon> <urq> <cme> <exe> <dde> <qye>

<rqc> <opc>

Status Register

*ESR?

<pon> <urq> <cme> <exe> <dde> <qye>

<rqc> <opc>

OR

*ESE

*ESE?

&

&

&

&

&

&

&

&

Enable

Register

| e7 | e6 | e5 | e4 | e3 | e2 | e1 | e0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

<esb> | # Positive transition sets status. | C0069 |

<pon> | power on |

|

<urq> | user request - not implemented in this product |

|

<cme> | command error |

|

<exe> | execution error |

|

<dde> | device dependent error |

|

<qye> | query error |

|

<rqc> | request control - not implemented in this product |

|

<opc> | operation complete - set in response to the *OPC command for |

|

| synchronization. |

|

<esb> | standard event register summary bit |

|