STATUS BYTE

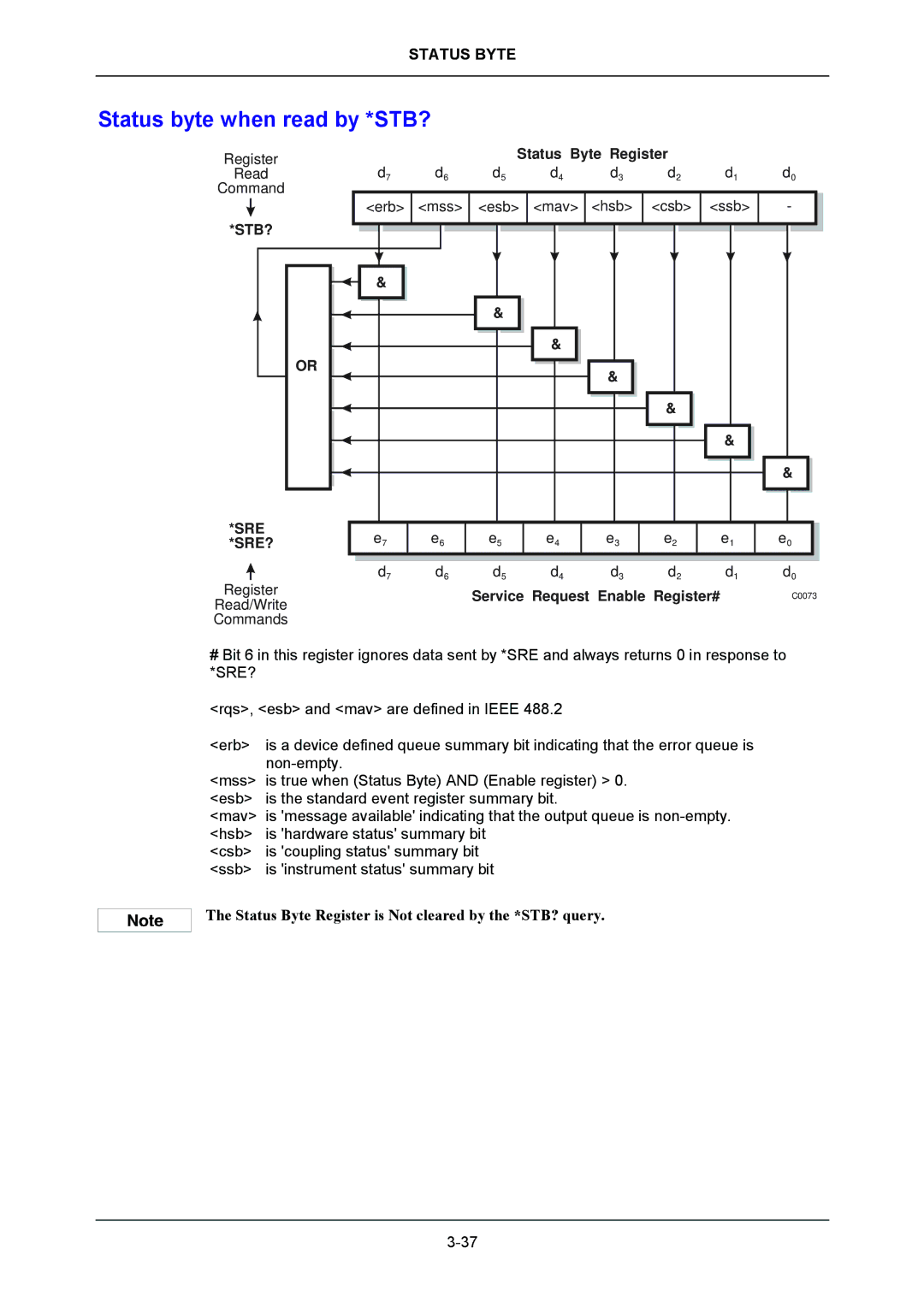

Status byte when read by *STB?

Register

Read

Command

*STB?

|

|

|

| Status Byte Register |

|

|

| |||

| d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 | ||

|

|

|

|

|

|

|

|

|

|

|

| <erb> | <mss> | <esb> | <mav> | <hsb> | <csb> | <ssb> | - |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OR

*SRE

*SRE?

Register

Read/Write

Commands

& |

& |

& |

& |

& |

& |

& |

e7 | e6 | e5 | e4 | e3 | e2 |

| e1 | e0 |

|

|

|

|

|

|

|

|

|

|

|

d7 | d6 | d5 | d4 | d3 | d2 | d1 | d0 | ||

|

| Service Request Enable Register# |

| C0073 | |||||

#Bit 6 in this register ignores data sent by *SRE and always returns 0 in response to *SRE?

<rqs>, <esb> and <mav> are defined in IEEE 488.2

<erb> | is a device defined queue summary bit indicating that the error queue is |

| |

<mss> | is true when (Status Byte) AND (Enable register) > 0. |

<esb> | is the standard event register summary bit. |

<mav> | is 'message available' indicating that the output queue is |

<hsb> | is 'hardware status' summary bit |

<csb> | is 'coupling status' summary bit |

<ssb> | is 'instrument status' summary bit |

The Status Byte Register is Not cleared by the *STB? query.