R

Chapter 3

Family Specific Considerations

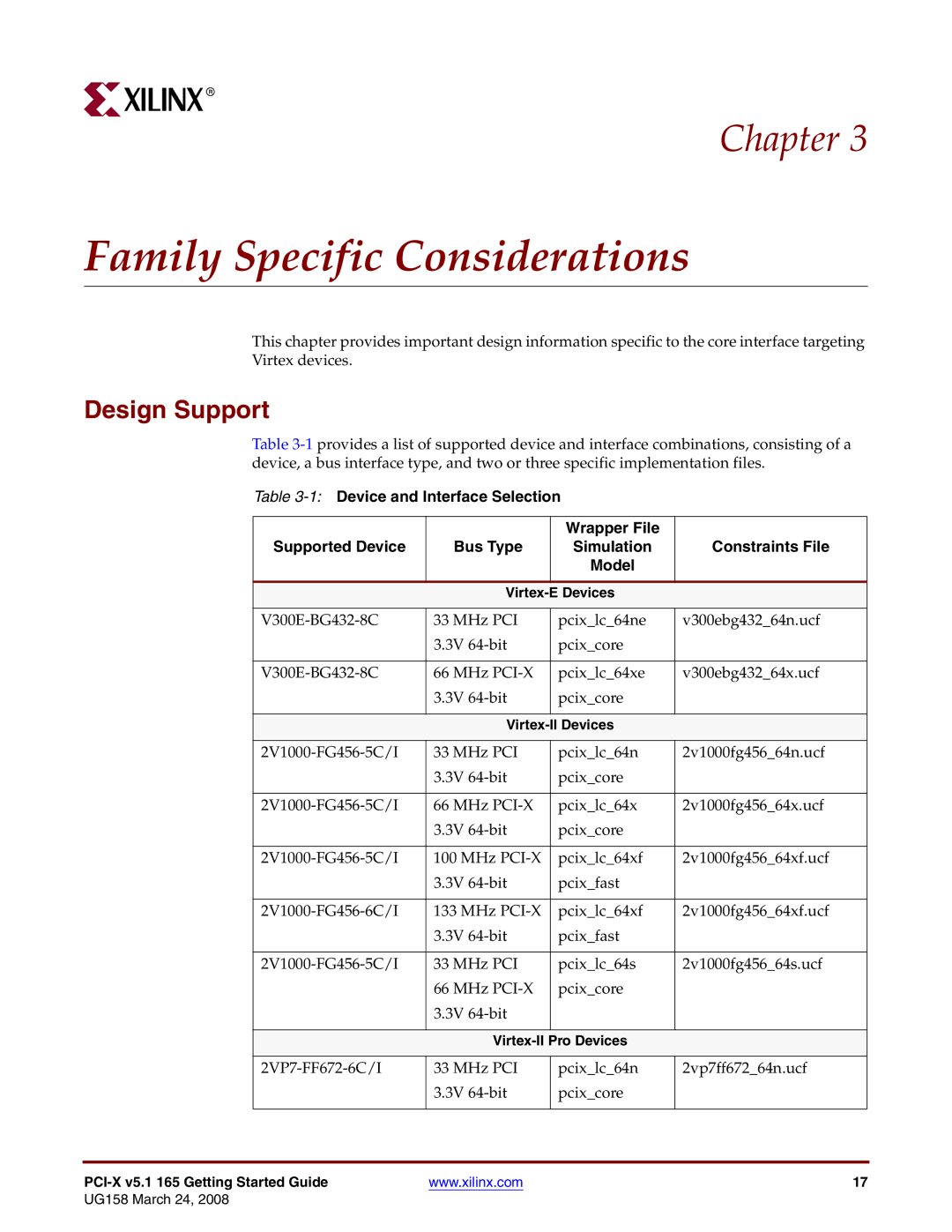

This chapter provides important design information specific to the core interface targeting Virtex devices.

Design Support

Table

Table

Supported Device

Bus Type

Wrapper File

Simulation

Model

Constraints File

33 MHz PCI | pcix_lc_64ne | v300ebg432_64n.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

66 MHz | pcix_lc_64xe | v300ebg432_64x.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

|

| ||

|

|

|

|

33 MHz PCI | pcix_lc_64n | 2v1000fg456_64n.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

66 MHz | pcix_lc_64x | 2v1000fg456_64x.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

100 MHz | pcix_lc_64xf | 2v1000fg456_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

133 MHz | pcix_lc_64xf | 2v1000fg456_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

33 MHz PCI | pcix_lc_64s | 2v1000fg456_64s.ucf | |

| 66 MHz | pcix_core |

|

| 3.3V |

|

|

|

|

|

|

|

| ||

33 MHz PCI

3.3V

pcix_lc_64n pcix_core

2vp7ff672_64n.ucf

| www.xilinx.com | 17 |

UG158 March 24, 2008