R

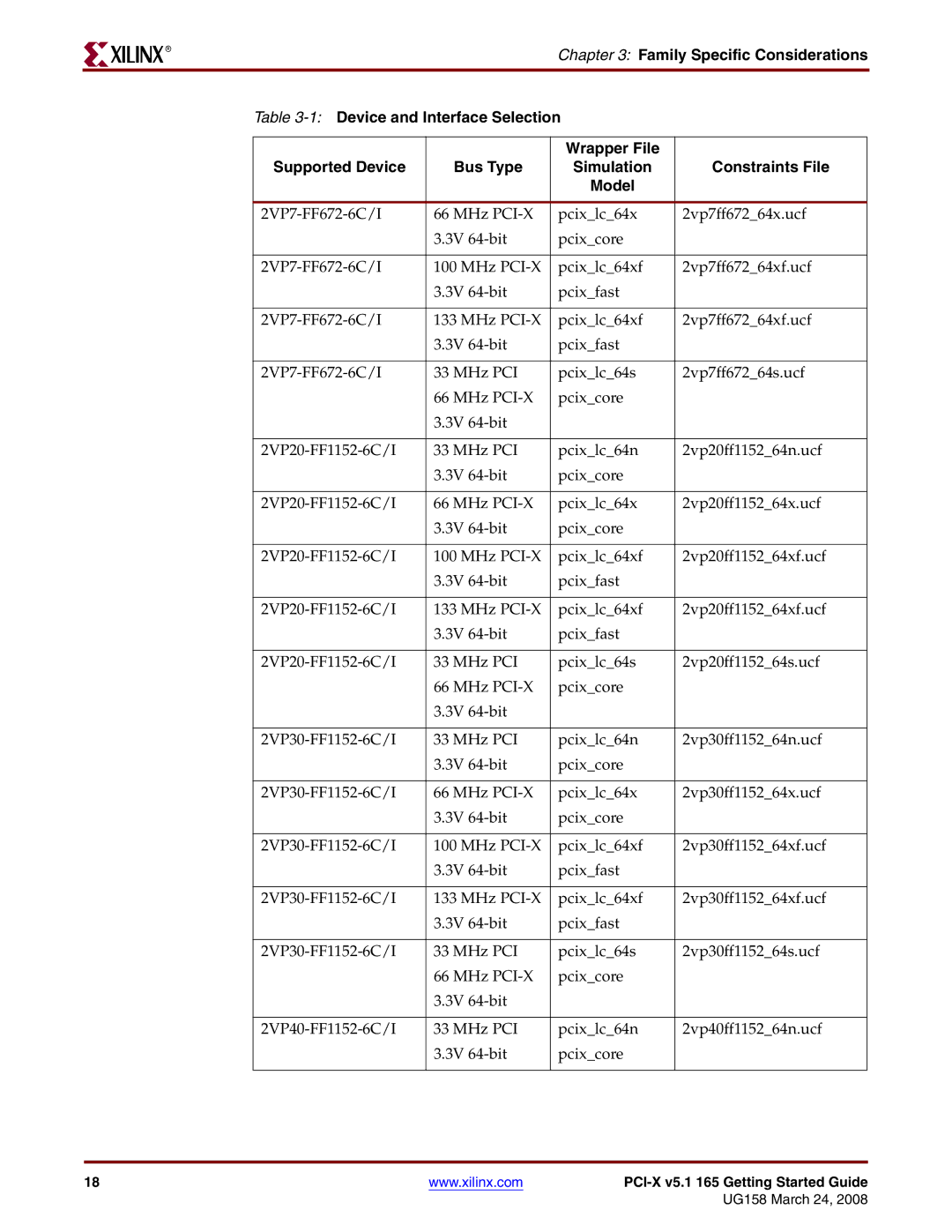

Chapter 3: Family Specific Considerations

Table

|

| Wrapper File |

|

Supported Device | Bus Type | Simulation | Constraints File |

|

| Model |

|

|

|

|

|

66 MHz | pcix_lc_64x | 2vp7ff672_64x.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

100 MHz | pcix_lc_64xf | 2vp7ff672_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

133 MHz | pcix_lc_64xf | 2vp7ff672_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

33 MHz PCI | pcix_lc_64s | 2vp7ff672_64s.ucf | |

| 66 MHz | pcix_core |

|

| 3.3V |

|

|

|

|

|

|

33 MHz PCI | pcix_lc_64n | 2vp20ff1152_64n.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

66 MHz | pcix_lc_64x | 2vp20ff1152_64x.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

100 MHz | pcix_lc_64xf | 2vp20ff1152_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

133 MHz | pcix_lc_64xf | 2vp20ff1152_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

33 MHz PCI | pcix_lc_64s | 2vp20ff1152_64s.ucf | |

| 66 MHz | pcix_core |

|

| 3.3V |

|

|

|

|

|

|

33 MHz PCI | pcix_lc_64n | 2vp30ff1152_64n.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

66 MHz | pcix_lc_64x | 2vp30ff1152_64x.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

100 MHz | pcix_lc_64xf | 2vp30ff1152_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

133 MHz | pcix_lc_64xf | 2vp30ff1152_64xf.ucf | |

| 3.3V | pcix_fast |

|

|

|

|

|

33 MHz PCI | pcix_lc_64s | 2vp30ff1152_64s.ucf | |

| 66 MHz | pcix_core |

|

| 3.3V |

|

|

|

|

|

|

33 MHz PCI | pcix_lc_64n | 2vp40ff1152_64n.ucf | |

| 3.3V | pcix_core |

|

|

|

|

|

18 | www.xilinx.com |

|

|

| UG158 March 24, 2008 |