Detailed Description

References

See the Marvell Alaska Gigabit Ethernet Transceiver product page for more information at http://www.marvell.com/products/transceivers/alaska_gigabit/index.jsp.

Also, see the Xilinx

6. USB-to-UART Bridge

The SP601 contains a Silicon Labs CP2103GM

Xilinx UART IP is expected to be implemented in the FPGA fabric. The FPGA supports the

Silicon Labs provides

Table

USB Connector | Signal Name | Description | |

Pin | |||

|

| ||

|

|

| |

1 | VBUS | +5V from host system (not used) | |

|

|

| |

2 | USB_DATA_N | Bidirectional differential serial data | |

|

|

| |

3 | USB_DATA_P | Bidirectional differential serial data | |

|

|

| |

4 | GROUND | Signal ground | |

|

|

|

Table | CP2103GM Connections |

|

| |

|

|

|

|

|

FPGA U1 |

| Schematic Netname | U4 CP2103GM |

|

Pin |

|

| ||

|

|

|

| |

|

|

|

|

|

U10 |

| USB_1_CTS | 22 |

|

|

|

|

|

|

T5 |

| USB_1_RTS | 23 |

|

|

|

|

|

|

L12 |

| USB_1_RX | 24 |

|

|

|

|

|

|

K14 |

| USB_1_TX | 25 |

|

|

|

|

| |

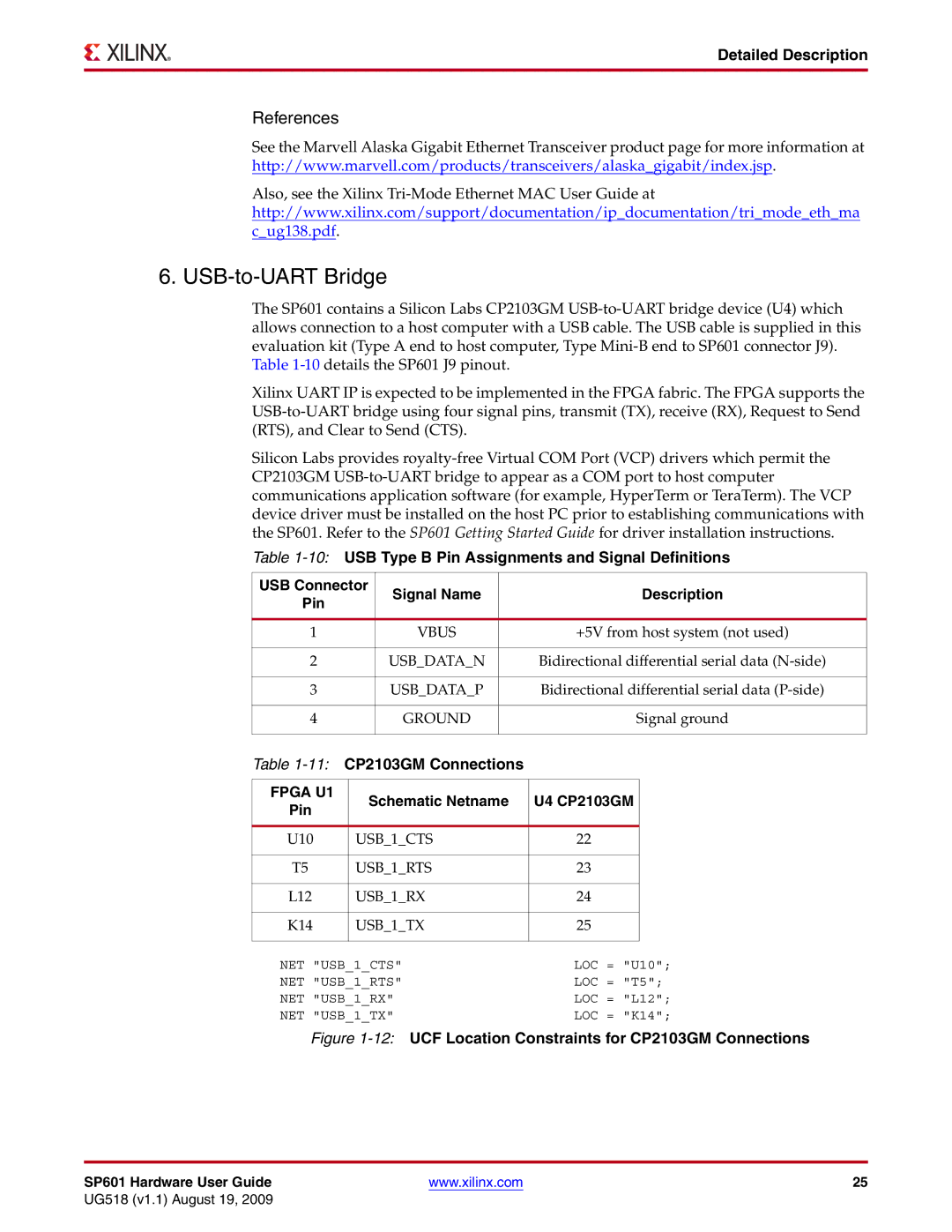

NET "USB_1_CTS" | LOC = "U10"; | |||

NET "USB_1_RTS" | LOC = "T5"; | |||

NET "USB_1_RX" | LOC = "L12"; | |||

NET "USB_1_TX" | LOC = "K14"; | |||

Figure 1-12: UCF Location Constraints for CP2103GM Connections

SP601 Hardware User Guide | www.xilinx.com | 25 |

UG518 (v1.1) August 19, 2009