Appendix D

SP601 Master UCF

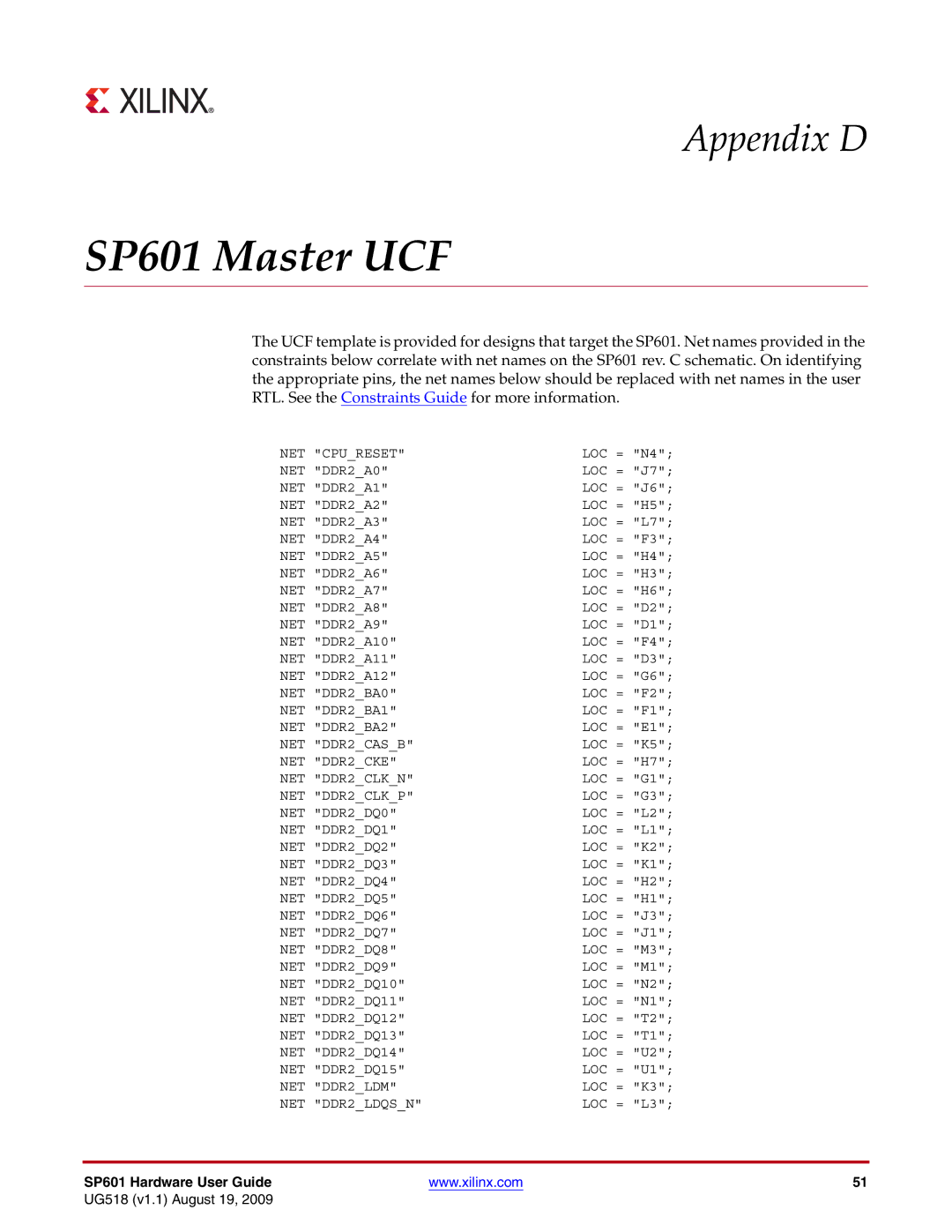

The UCF template is provided for designs that target the SP601. Net names provided in the constraints below correlate with net names on the SP601 rev. C schematic. On identifying the appropriate pins, the net names below should be replaced with net names in the user RTL. See the Constraints Guide for more information.

NET "CPU_RESET" NET "DDR2_A0" NET "DDR2_A1" NET "DDR2_A2" NET "DDR2_A3" NET "DDR2_A4" NET "DDR2_A5" NET "DDR2_A6" NET "DDR2_A7" NET "DDR2_A8" NET "DDR2_A9" NET "DDR2_A10" NET "DDR2_A11" NET "DDR2_A12" NET "DDR2_BA0" NET "DDR2_BA1" NET "DDR2_BA2" NET "DDR2_CAS_B" NET "DDR2_CKE" NET "DDR2_CLK_N" NET "DDR2_CLK_P" NET "DDR2_DQ0" NET "DDR2_DQ1" NET "DDR2_DQ2" NET "DDR2_DQ3" NET "DDR2_DQ4" NET "DDR2_DQ5" NET "DDR2_DQ6" NET "DDR2_DQ7" NET "DDR2_DQ8" NET "DDR2_DQ9" NET "DDR2_DQ10" NET "DDR2_DQ11" NET "DDR2_DQ12" NET "DDR2_DQ13" NET "DDR2_DQ14" NET "DDR2_DQ15" NET "DDR2_LDM" NET "DDR2_LDQS_N"

LOC = "N4"; LOC = "J7"; LOC = "J6"; LOC = "H5"; LOC = "L7"; LOC = "F3"; LOC = "H4"; LOC = "H3"; LOC = "H6"; LOC = "D2"; LOC = "D1"; LOC = "F4"; LOC = "D3"; LOC = "G6"; LOC = "F2"; LOC = "F1"; LOC = "E1"; LOC = "K5"; LOC = "H7"; LOC = "G1"; LOC = "G3"; LOC = "L2"; LOC = "L1"; LOC = "K2"; LOC = "K1"; LOC = "H2"; LOC = "H1"; LOC = "J3"; LOC = "J1"; LOC = "M3"; LOC = "M1"; LOC = "N2"; LOC = "N1"; LOC = "T2"; LOC = "T1"; LOC = "U2"; LOC = "U1"; LOC = "K3"; LOC = "L3";

SP601 Hardware User Guide | www.xilinx.com | 51 |

UG518 (v1.1) August 19, 2009