Chapter 1: SP601 Evaluation Board

GPIO Male Pin Header

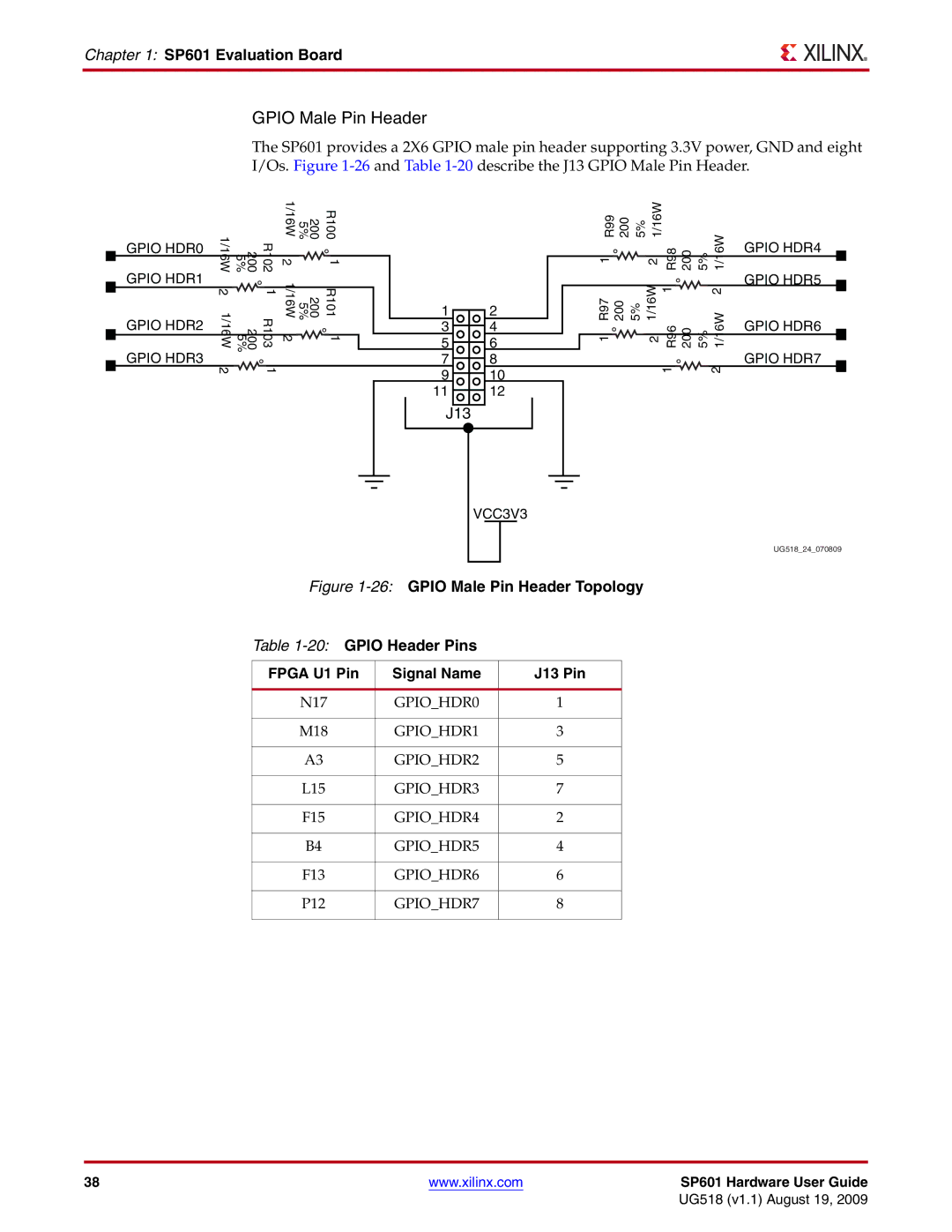

The SP601 provides a 2X6 GPIO male pin header supporting 3.3V power, GND and eight I/Os. Figure

GPIO HDR0

GPIO HDR1

GPIO HDR2

GPIO HDR3

1/16W |

| R102 | 1/16W | 200 5% | R100 |

200 5% | 2 | 1 | |||

2 |

| 1 | 1/16W | 200 5% | R101 |

1/16W | 200 5% | R103 | 2 | 1 | |

2 |

| 1 |

|

|

|

1 2

3 4

5 6

78

910

11 12

J13

R99 | 200 | 5% | 1/16W |

|

|

| 1/16W |

1 | 2 | R98 | 200 | 5% | |||

1 R97 | 200 | 5% | 1/16W | 1 |

|

| 2 |

2 | R96 | 200 | 5% | 1/16W | |||

|

|

|

| 1 |

|

| 2 |

GPIO HDR4

GPIO HDR5

GPIO HDR6

GPIO HDR7

VCC3V3

UG518_24_070809

Figure 1-26: GPIO Male Pin Header Topology

Table 1-20: GPIO Header Pins

FPGA U1 Pin | Signal Name | J13 Pin |

|

|

|

N17 | GPIO_HDR0 | 1 |

|

|

|

M18 | GPIO_HDR1 | 3 |

|

|

|

A3 | GPIO_HDR2 | 5 |

|

|

|

L15 | GPIO_HDR3 | 7 |

|

|

|

F15 | GPIO_HDR4 | 2 |

|

|

|

B4 | GPIO_HDR5 | 4 |

|

|

|

F13 | GPIO_HDR6 | 6 |

|

|

|

P12 | GPIO_HDR7 | 8 |

|

|

|

38 | www.xilinx.com | SP601 Hardware User Guide |

|

| UG518 (v1.1) August 19, 2009 |