Detailed Description

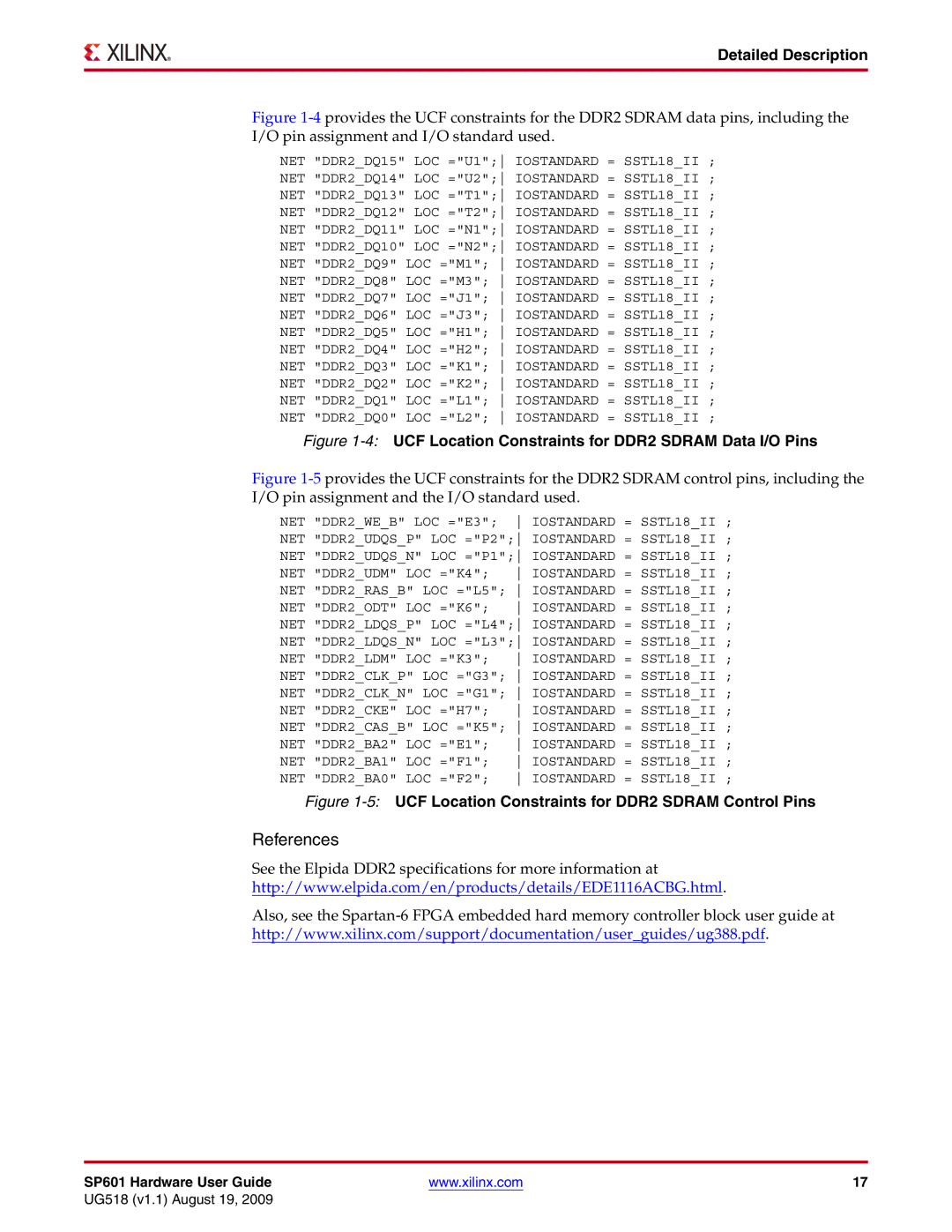

Figure 1-4 provides the UCF constraints for the DDR2 SDRAM data pins, including the I/O pin assignment and I/O standard used.

NET "DDR2_DQ15" LOC ="U1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ14" LOC ="U2"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ13" LOC ="T1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ12" LOC ="T2"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ11" LOC ="N1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ10" LOC ="N2"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ9" LOC ="M1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ8" LOC ="M3"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ7" LOC ="J1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ6" LOC ="J3"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ5" LOC ="H1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ4" LOC ="H2"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ3" LOC ="K1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ2" LOC ="K2"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ1" LOC ="L1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_DQ0" LOC ="L2"; IOSTANDARD = SSTL18_II ;

Figure 1-4: UCF Location Constraints for DDR2 SDRAM Data I/O Pins

Figure 1-5 provides the UCF constraints for the DDR2 SDRAM control pins, including the I/O pin assignment and the I/O standard used.

NET "DDR2_WE_B" LOC ="E3"; IOSTANDARD = SSTL18_II ;

NET "DDR2_UDQS_P" LOC ="P2"; IOSTANDARD = SSTL18_II ;

NET "DDR2_UDQS_N" LOC ="P1"; IOSTANDARD = SSTL18_II ;

NET "DDR2_UDM" LOC ="K4"; | IOSTANDARD = SSTL18_II ; |

NET "DDR2_RAS_B" LOC ="L5"; IOSTANDARD = SSTL18_II ; | |

NET "DDR2_ODT" LOC ="K6"; | IOSTANDARD = SSTL18_II ; |

NET "DDR2_LDQS_P" LOC ="L4"; IOSTANDARD = SSTL18_II ; | |

NET "DDR2_LDQS_N" LOC ="L3"; IOSTANDARD = SSTL18_II ; | |

NET "DDR2_LDM" LOC ="K3"; | IOSTANDARD = SSTL18_II ; |

NET "DDR2_CLK_P" LOC ="G3"; IOSTANDARD = SSTL18_II ; | |

NET "DDR2_CLK_N" LOC ="G1"; IOSTANDARD = SSTL18_II ; | |

NET "DDR2_CKE" LOC ="H7"; | IOSTANDARD = SSTL18_II ; |

NET "DDR2_CAS_B" LOC ="K5"; IOSTANDARD = SSTL18_II ; | |

NET "DDR2_BA2" LOC ="E1"; | IOSTANDARD = SSTL18_II ; |

NET "DDR2_BA1" LOC ="F1"; | IOSTANDARD = SSTL18_II ; |

NET "DDR2_BA0" LOC ="F2"; | IOSTANDARD = SSTL18_II ; |

Figure 1-5: UCF Location Constraints for DDR2 SDRAM Control Pins

References

See the Elpida DDR2 specifications for more information at

http://www.elpida.com/en/products/details/EDE1116ACBG.html.

Also, see the

http://www.xilinx.com/support/documentation/user_guides/ug388.pdf.

SP601 Hardware User Guide | www.xilinx.com | 17 |

UG518 (v1.1) August 19, 2009