Chapter 1: SP601 Evaluation Board

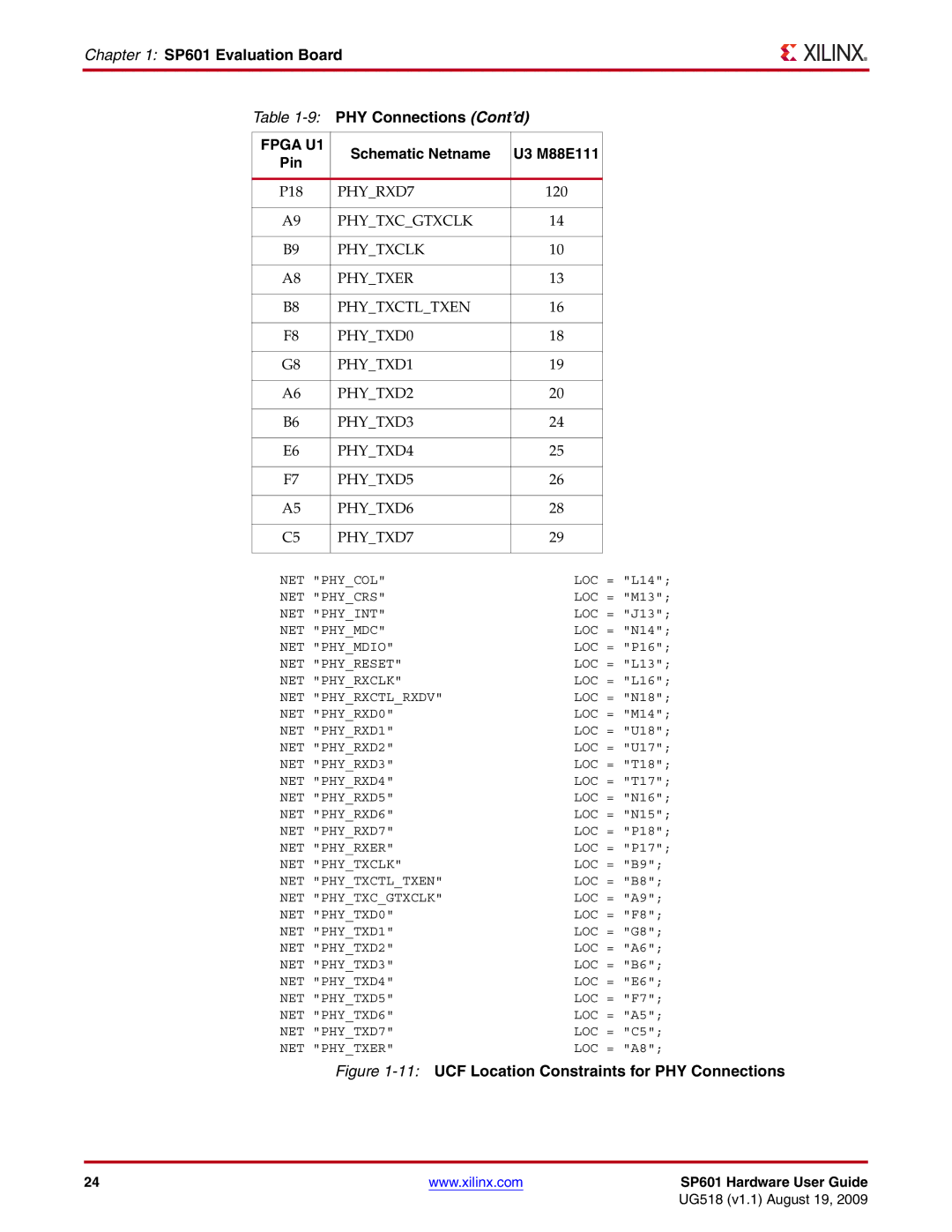

Table 1-9: PHY Connections (Cont’d)

FPGA U1 | Schematic Netname | U3 M88E111 | |

Pin | |||

|

| ||

|

|

| |

P18 | PHY_RXD7 | 120 | |

|

|

| |

A9 | PHY_TXC_GTXCLK | 14 | |

|

|

| |

B9 | PHY_TXCLK | 10 | |

|

|

| |

A8 | PHY_TXER | 13 | |

|

|

| |

B8 | PHY_TXCTL_TXEN | 16 | |

|

|

| |

F8 | PHY_TXD0 | 18 | |

|

|

| |

G8 | PHY_TXD1 | 19 | |

|

|

| |

A6 | PHY_TXD2 | 20 | |

|

|

| |

B6 | PHY_TXD3 | 24 | |

|

|

| |

E6 | PHY_TXD4 | 25 | |

|

|

| |

F7 | PHY_TXD5 | 26 | |

|

|

| |

A5 | PHY_TXD6 | 28 | |

|

|

| |

C5 | PHY_TXD7 | 29 | |

|

|

|

NET "PHY_COL" | LOC = "L14"; |

NET "PHY_CRS" | LOC = "M13"; |

NET "PHY_INT" | LOC = "J13"; |

NET "PHY_MDC" | LOC = "N14"; |

NET "PHY_MDIO" | LOC = "P16"; |

NET "PHY_RESET" | LOC = "L13"; |

NET "PHY_RXCLK" | LOC = "L16"; |

NET "PHY_RXCTL_RXDV" | LOC = "N18"; |

NET "PHY_RXD0" | LOC = "M14"; |

NET "PHY_RXD1" | LOC = "U18"; |

NET "PHY_RXD2" | LOC = "U17"; |

NET "PHY_RXD3" | LOC = "T18"; |

NET "PHY_RXD4" | LOC = "T17"; |

NET "PHY_RXD5" | LOC = "N16"; |

NET "PHY_RXD6" | LOC = "N15"; |

NET "PHY_RXD7" | LOC = "P18"; |

NET "PHY_RXER" | LOC = "P17"; |

NET "PHY_TXCLK" | LOC = "B9"; |

NET "PHY_TXCTL_TXEN" | LOC = "B8"; |

NET "PHY_TXC_GTXCLK" | LOC = "A9"; |

NET "PHY_TXD0" | LOC = "F8"; |

NET "PHY_TXD1" | LOC = "G8"; |

NET "PHY_TXD2" | LOC = "A6"; |

NET "PHY_TXD3" | LOC = "B6"; |

NET "PHY_TXD4" | LOC = "E6"; |

NET "PHY_TXD5" | LOC = "F7"; |

NET "PHY_TXD6" | LOC = "A5"; |

NET "PHY_TXD7" | LOC = "C5"; |

NET "PHY_TXER" | LOC = "A8"; |

Figure 1-11: UCF Location Constraints for PHY Connections

24 | www.xilinx.com | SP601 Hardware User Guide |

|

| UG518 (v1.1) August 19, 2009 |