AMD SimNow Simulator

Trademarks

Contents

2.5

22.1.1

Cpuid

223

Viii

Figures

7Graphics-Device VGA Sub Device Properties Dialog

Tables

Xii

Overview

Overview

System Requirements

Installation

Installation Procedure

Setting up Linux for the Simulator

Directory Structure and Executable

Configuration File

Updates and Questions

Graphical User Interface

Tool Bar Buttons

Graphical User Interface

Device Window

Device Window

Add a New Device

Workspace Popup Menu

Add Connection

Workspace Popup Menu

Configure Device

Disconnect Device

Example Computer Description

Delete Device

Symbol Device Short Description

Device Window Quick Reference

Task Where to Find the Properties

Device Groups

Terms

Concept Diagrams

Working with Device Groups

Device Group 2 group devices 1 library device

Shell Automation Commands for Device Groups

Device Tree

Enabled vs. Disabled vs. Mixed

Device Group Examples

Example 1GB DDR2 memory

Example Quad-Core Node

12 Created Dimm Device Group

ID file amd-xxxx.id Graphical User Interface

Creating a Device Group GUI

Example SuperIO device

Figure ?

Child Device Name External Port Names Internal

Creating a Device Group Automation Commands

We can modify an existing created device group‟s options

Ungrouping a created device group

SimStats and Diagnostic Ports

Main Window

Real Mips Graph

CPU-Statistics Graphs

Translation Graph

PIO Rate Graph

Invalidation Rate Graph

Exception Rate Graph

Mmio Rate Graph

Simulated Video

Hard Disk and Floppy Display

Image Type File Extension

Using Hard Drive, DVD-/CD-ROM and Floppy Images

Registry Window

Help, Problems and Bug Reports

24 Registry Window

Disk Images

Creating a Blank Hard-Drive Image

2shows the DiskTool shell window

New Image Size

DiskTool Operation Successful

Argument Description

Command-Line Arguments

Running the Simulator

Open a Simulation Definition File

Main Window BSD Loaded

Installing an Operating System

Assigning Disk-Images

AMD Confidential

Installing WindowsXP

Run The Simulation

Interaction with the Simulated Machine

Simulation Reset

Multi-Machine Support

Following command creates a new simulation machine

This example exits the simulated machine „1‟

This page is intentionally blank

BSD Files

Device Placement

Create a Simulated Computer

Create a Simulated Computer

Solo.bsd Device Configuration

PCI Bus Configuration dialog window

Save and Run

Device Configuration

Symbol Device Public Release Full Release

AMD Confidential

Initialization and Reset State

Contents of a BSD

Configuration Options

AweSim Processor Device

AweSim Processor-Type Properties

Log Messages

Difference from Real Hardware

Debugger Device

Select View→Show Devices

Dimm Device

AMD Opteron Processor Virtual Bank-Select Line Configuration

Initialization/Reset State

DIMM-Bank Options Properties Dialog

Dimm Module Properties Dialog

This device does not produce log messages

VGA Sub Device Configuration

Emerald Graphics Device

Frame Buffer Sub Device Configuration

Supported Vesa Bios Graphics Modes

3shows the supported custom Vesa mode numbers

Improve Graphics Performance

Matrox MGA-G400 PCI/AGP

Ramdac

Interfaces

10 Matrox G400 Information Property Dialog

11 Matrox G400 Configuration Properties

Supported 2D Features

Supported DirectX 6.1 Features

Supported Graphics Modes

Memory Interface

Guest Operating System Device Driver Version Known Issues

Supported Guest Operating Systems

12 Enable Full Hardware Acceleration on WindowsXP guest

Enabling Hardware Cursor Support

Super IO Devices Winbond W83627HF SIO / ITE 8712 SIO

∙ Floppy ∙ COM1 and COM2 ∙ LPT1 ∙ IR

Floppy Configuration Options

Memory Device

14 Memory Configuration Properties Dialog

Difference from Real Hardware

PCA9548 SMB Device

Interface

16 PCA9556 SMB Configuration Properties Dialog

PCA9556 SMB Device

17and -18show configuration options for the Northbridge

AMD 8th Generation Integrated Northbridge Device

17 Northbridge Logging Capabilities Properties Dialog

19 Northbridge DDR2 Training Properties Dialog

Differences from Real Hardware

Common Configuration Options

AMD-8111 Southbridge Devices IO Hubs

20 USB Properties Dialog AMD-8111 Southbridge

21 Cmos Properties Dialog AMD-8111 Southbridge

Device Options

23 Device Options Properties Dialog AMD-8111 chipset

24 Logging Options Properties Dialog AMD-8111 chipset

25shows the PCI-Bus configuration options

PCI BUS Device

25 PCI Bus Properties Dialog

26 AMD-8131 Device Hot Plug Configuration

AMD-8131 PCI-XController

27 AMD-8132 Device Hot Plug Configuration

AMD-8132 PCI-XController

100

PCI-X Test Device

101

AMD-8151 AGP Bridge Device

29 AMD-8151 Device Properties Dialog

103

Raid Device Compaq SmartArray

SMB Hub Device

105

106

19 AT24C Device

107

Exdi Server Device

USB Keyboard and USB Mouse Devices

109

XTR Device

Using XTR

Recoding XTR Trace

Stop XTR Record

XTR Playback

Reset

Stop XTR Playback

Init from BSD

Init from Automation Script

113

XTR Structure

XML Structure

Defines an IOR or IOW dormant event

115

XTR Binary File Contents

ModeFlags

117

Limitations

Example XTR XML File

118

119

120

121

Data Length=2 Value=40af / /Event

122

JumpDrive Device

123

24 E1000 Network Adapter Device

32 Communication via Mediator

Simulated Link Negotiation

125

Switch Description

Mediator Daemon

Example Configurations

MAC Addresses for use with the Adapter

Absolute NIC

127

Client-Server simulated network

Isolated Client-Server simulated network Same process

Visibility Diagram

129

Plug and Play Monitor Device

35 Plug and Play Monitor Device Configuration

131

ATI SB400/SB600/SB700 Southbridge Devices

36 ATI SB600 Sata Configuration Dialog

133

ATI RS480/RS780/RD790/RD890 Northbridge Devices

AMD Istanbul Device

135

AMD Sao Paulo Device

AMD Magny-Cours Device

137

138

PCI Configuration Viewer

139

Modifying the PCI Configuration contents

Scanning PCI Buses

141

Logging

Message Log

142

Error Log

143

Log I/O Space Accesses

I/O Logging

Log Fastpath Memory Requests when Logging

145

146

Using the CPU Debugger

Setting a Breakpoint

CPU Debugger

147

Command Description

Single Stepping the Simulation

Stepping Over an Instruction

148

149

Skipping an Instruction

Viewing a Memory Region

Reading PCI Configuration Registers

Reading CPU MSR Contents

151

Debugger Command Reference

Find Pattern in Memory

Debugger Command Definition

152

Address

153

154

155

Debug Interface

Kernel Debugger

156

GDB Interface

Simple Approach

Using Another Port on the Same Machine

Using Two Separate Machines

Linux Host Serial Port Communication

Alternate Approach

158

Command API

GetLastError

Exec

159

160

Command-Line Mode

DiskTool

Option

Syntax

GUI Mode

162

163

164

DiskTool GUI Window

165

DiskTool Progress Window

166

Bios Developer’s Quick Start Guide

Loading a Bios Image

Changing Dram Size

167

Changing SPD Data

168

169

Logging PCI Configuration Cycles

Clearing Cmos

Logging CPU Cycles

170

Creating a Floppy-Disk Image

171

172

Frequently Asked Questions FAQ

173

What devices are supported?

Why doesn’t the OS find a connected USB device?

175

176

177

Appendix

Format of Floppy and Hard-Drive Images

Device Files *.BSL

Bill of Material

Computer Platform Files BSD

179

Product Files *.ID

Image Files *.HDD, *.FDD, *.ROM, *.SPD, *.BIN

Memory SPD Files

Supported Guest Operating Systems

181

Cpuid Standard Feature Support Standard Function

Cpuid

Cpuid AMD Feature Support Extended Function

183

Known Issues

185

Instruction Reference

Notation

187

Opcode Syntax

General Purpose Instructions

189

Reg/mem8,imm8

Reg/mem8

Imm8 Reg/mem16,imm16

Imm16 Reg/mem32,imm32

191

Call rel16off

Call rel32off

Call reg/mem16

By reg/mem16 Call reg/mem32

193

Cmovl reg64,reg/mem64

Cmovnge reg16,reg/mem16

Cmovnge reg32,reg/mem32

Cmovnge reg64,reg/mem64

195

DEC reg/mem8

DEC reg/mem16

DEC reg/mem32

DEC reg/mem64

197

INC reg/mem8

INC reg/mem16

INC reg/mem32

INC reg/mem64

199

JP rel16off

JP rel32off

JPE rel8off

JPE rel16off

201

Loop rel8off

Loope rel8off

Loopz rel8off

MOV reg/mem8,reg8

203

Movsx reg16,reg/mem8

Movsx reg32,reg/mem8

Movsx reg64,reg/mem8

Movsx reg32,reg/mem16

205

POP reg/mem16

POP reg/mem32

POP reg/mem64

POP reg16 +rw

207

RCL reg/mem32,1

RCL reg/mem32,CL

RCL reg/mem32,imm8

RCL reg/mem64,1

209

ROR reg/imm32,1

ROR reg/mem32,CL

ROR reg/mem32,imm8

ROR reg/imm64,1

211

SBB reg/mem8,imm8

SBB reg/mem16,imm16

SBB reg/mem32,imm32

SBB reg/mem64,imm32

213

Shld reg/mem16,reg16,imm8

Shld reg/mem16,reg16,CL

Shld reg/mem32,reg32,imm8

Shld reg/me326,reg32,CL

215

SUB reg/mem8,imm8

SUB reg/mem16,imm16

SUB reg/mem32,imm32

SUB reg/mem64,imm32

217

Test reg/mem64,reg64

Xadd reg/mem8,reg8

Xadd reg/mem16,reg16

Xadd reg/mem32,reg32

219

System Instructions

221

Opcode Instruction Description

223

Virtualization Instruction Reference

5 64-Bit Media Instruction Reference

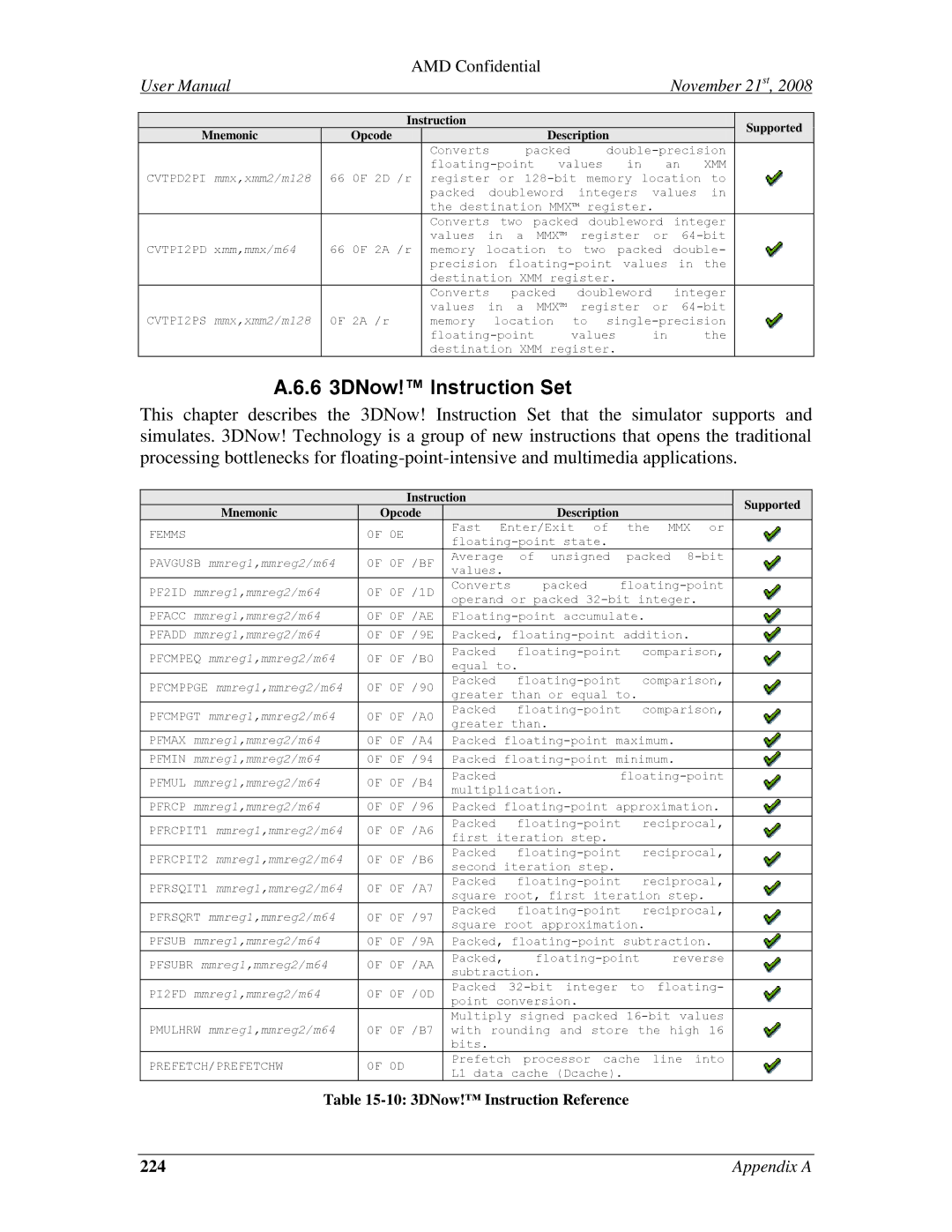

6 3DNow! Instruction Set

225

Extension to the 3DNow! Instruction Set

Prescott New Instructions

Movddup xmm1,xmm2/m64

Setup Monitor Address

Monitor Wait

Automation Commands

227

Automation Command Description

Shell

Automation Command Description

229

Tool Bar Buttons, on

231

2 IDE

Example, GetLogIO USB Jumpdrive returns

3 USB

233

Cmos

Acpi

Floppy

Debug

AMD-8151 AGP Bridge

9 VGA

Serial

235

„false‟

HyperTransport Technology Configuration

237

8th Generation Northbridge

AMD-8111 Device

Journal

239

240

241

Command Args Description

Emerald Graphics

21 SIO

Matrox MGA-G400 Graphics

PCI Bus

Memory Device

243

Raid

Dimm

245

Keyboard and Mouse

Maximum range 0

247

JumpDrive

Prefix Action

To initialize the JumpDrive, and copy data to it

249

27 E1000

28 XTR

251

ATI SB400/SB600/SB700

ATI RS480

ATI RD890S/RD890/RD780S/RX880

ATI RS780

ATI RD790/RD780/RX780

253

254

Index

255

256

257