ADSP-TS201S

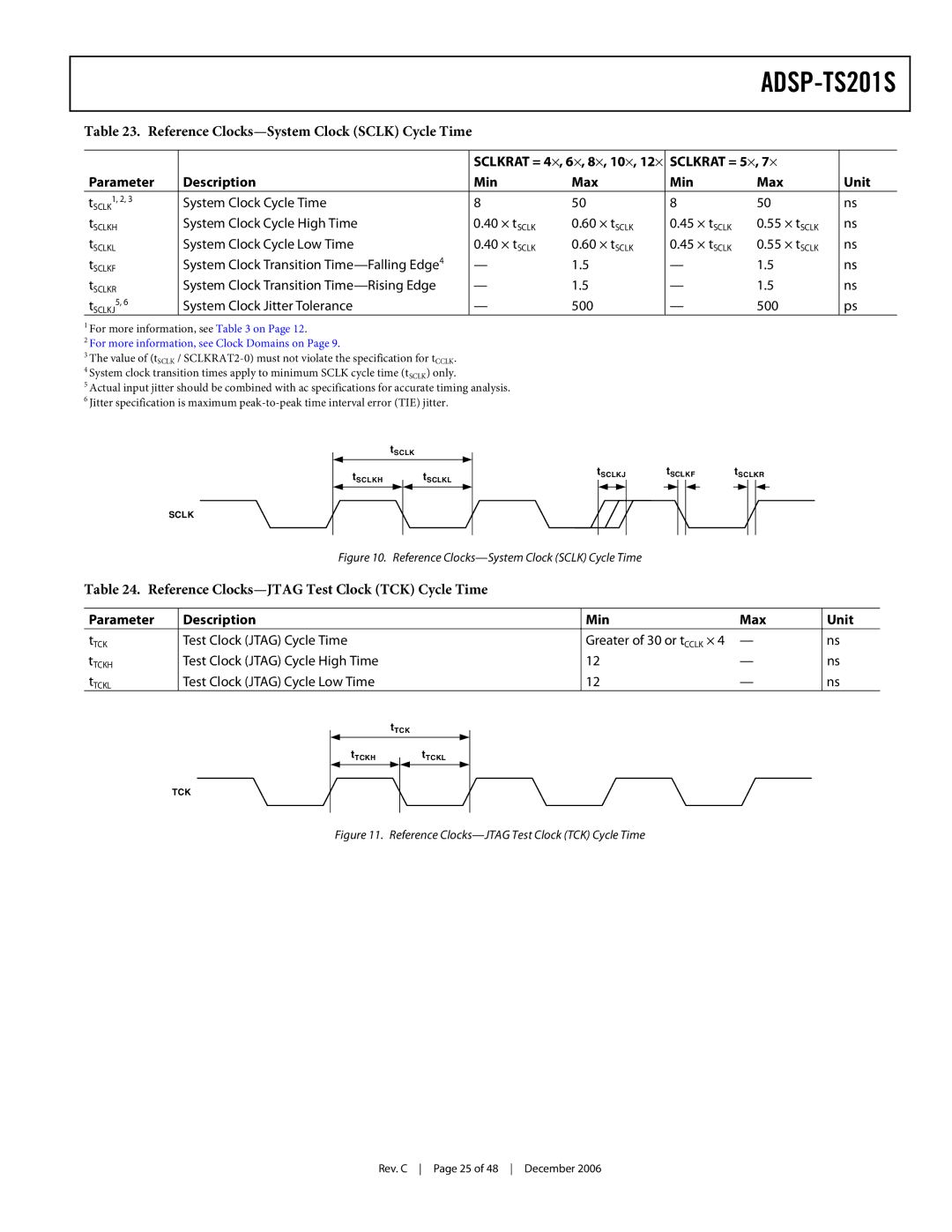

Table 23. Reference Clocks—System Clock (SCLK) Cycle Time

|

| SCLKRAT = 4⋅, 6⋅, 8⋅, 10⋅, 12⋅ | SCLKRAT = 5⋅, 7⋅ |

| ||

Parameter | Description | Min | Max | Min | Max | Unit |

1, 2, 3 | System Clock Cycle Time | 8 | 50 | 8 | 50 | ns |

tSCLK | ||||||

tSCLKH | System Clock Cycle High Time | 0.40 × tSCLK | 0.60 × tSCLK | 0.45 × tSCLK | 0.55 × tSCLK | ns |

tSCLKL | System Clock Cycle Low Time | 0.40 × tSCLK | 0.60 × tSCLK | 0.45 × tSCLK | 0.55 × tSCLK | ns |

tSCLKF | System Clock Transition | — | 1.5 | — | 1.5 | ns |

tSCLKR | System Clock Transition | — | 1.5 | — | 1.5 | ns |

5, 6 | System Clock Jitter Tolerance | — | 500 | — | 500 | ps |

tSCLKJ | ||||||

1For more information, see Table 3 on Page 12.

2For more information, see Clock Domains on Page 9.

3The value of (tSCLK /

4 System clock transition times apply to minimum SCLK cycle time (tSCLK) only.

5 Actual input jitter should be combined with ac specifications for accurate timing analysis. 6 Jitter specification is maximum

SCLK

tSCLK

tSCLKH tSCLKL

tSCLKJ tSCLKF tSCLKR

Figure 10. Reference Clocks—System Clock (SCLK) Cycle Time

Table 24. Reference Clocks—JTAG Test Clock (TCK) Cycle Time

Parameter | Description | Min | Max | Unit |

tTCK | Test Clock (JTAG) Cycle Time | Greater of 30 or tCCLK × 4 | — | ns |

tTCKH | Test Clock (JTAG) Cycle High Time | 12 | — | ns |

tTCKL | Test Clock (JTAG) Cycle Low Time | 12 | — | ns |

tTCK

tTCKH

tTCKL

TCK

Figure 11. Reference Clocks—JTAG Test Clock (TCK) Cycle Time

Rev. C Page 25 of 48 December 2006