ADSP-TS201S

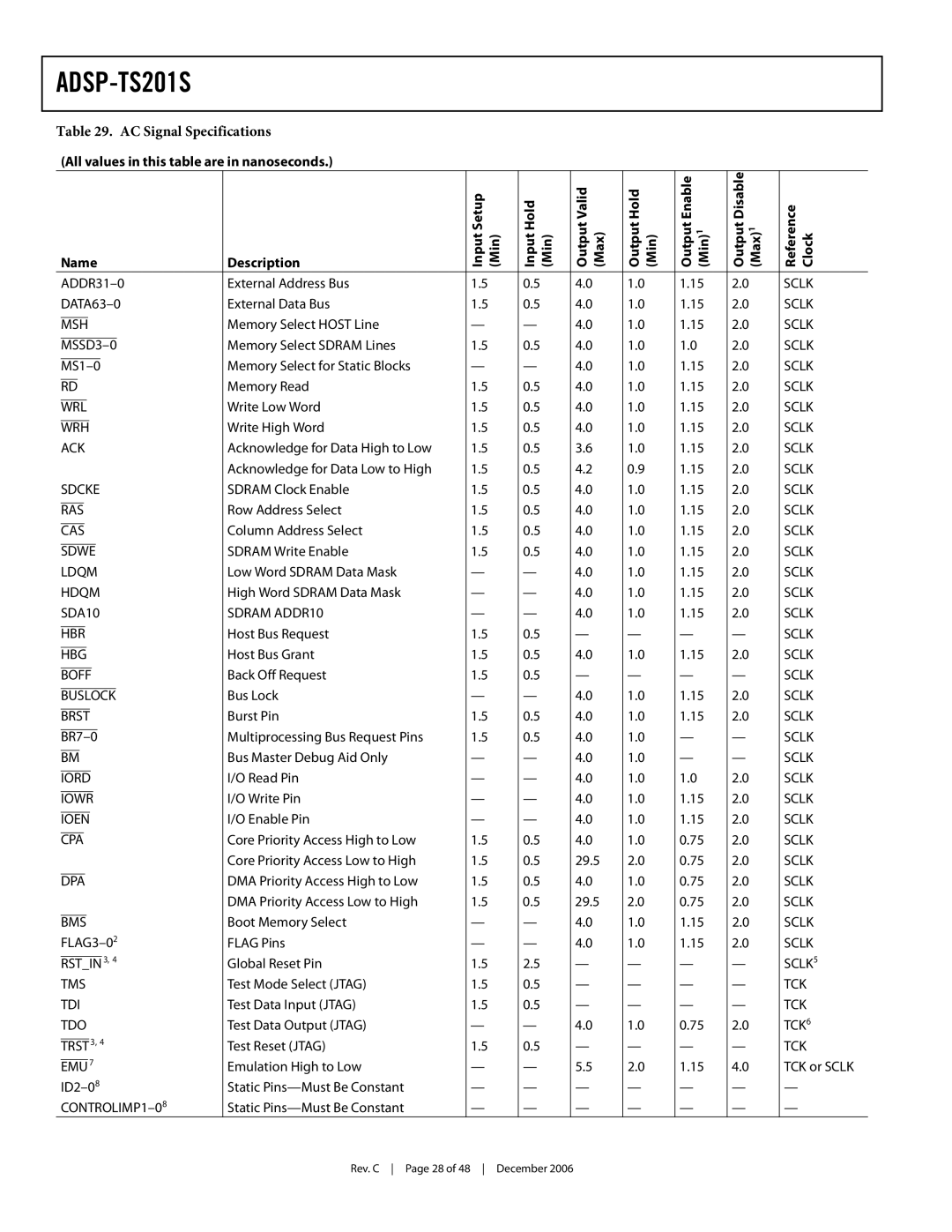

Table 29. AC Signal Specifications

(All values in this table are in nanoseconds.)

Name | Description | ||||||||||||||||||||||||

External Address Bus | |||||||||||||||||||||||||

External Data Bus | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Memory Select HOST Line |

MSH | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Memory Select SDRAM Lines | |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Memory Select for Static Blocks | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Memory Read | |||

RD | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Write Low Word | ||||

WRL | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Write High Word | |||||

WRH | |||||||||||||||||||||||||

ACK | Acknowledge for Data High to Low | ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Acknowledge for Data Low to High |

SDCKE | SDRAM Clock Enable | ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Row Address Select | ||||||

RAS | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Column Address Select | |||||||

CAS | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SDRAM Write Enable | ||||||||

SDWE | |||||||||||||||||||||||||

LDQM | Low Word SDRAM Data Mask | ||||||||||||||||||||||||

HDQM | High Word SDRAM Data Mask | ||||||||||||||||||||||||

SDA10 | SDRAM ADDR10 | ||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Host Bus Request | |||||||||

HBR | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Host Bus Grant | ||||||||||

HBG | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| Back Off Request | |||||||||||

BOFF | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| Bus Lock | ||||||||||||

BUSLOCK | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| Burst Pin | |||||||||||||

BRST | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

| Multiprocessing Bus Request Pins | ||||||||||||||

| |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

| Bus Master Debug Aid Only | |||||||||||||||

BM | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

| I/O Read Pin | ||||||||||||||||

IORD | |||||||||||||||||||||||||

|

|

|

|

|

|

|

| I/O Write Pin | |||||||||||||||||

IOWR | |||||||||||||||||||||||||

|

|

|

|

|

|

| I/O Enable Pin | ||||||||||||||||||

IOEN | |||||||||||||||||||||||||

|

|

|

|

|

| Core Priority Access High to Low | |||||||||||||||||||

CPA | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Core Priority Access Low to High |

|

|

|

|

| DMA Priority Access High to Low | ||||||||||||||||||||

DPA | |||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| DMA Priority Access Low to High |

|

|

|

|

| Boot Memory Select | ||||||||||||||||||||

BMS | |||||||||||||||||||||||||

FLAG Pins | |||||||||||||||||||||||||

|

|

| 3, 4 | Global Reset Pin | |||||||||||||||||||||

RST_IN | |||||||||||||||||||||||||

TMS | Test Mode Select (JTAG) | ||||||||||||||||||||||||

TDI | Test Data Input (JTAG) | ||||||||||||||||||||||||

TDO | Test Data Output (JTAG) | ||||||||||||||||||||||||

|

| 3, 4 | Test Reset (JTAG) | ||||||||||||||||||||||

TRST | |||||||||||||||||||||||||

| 7 | Emulation High to Low | |||||||||||||||||||||||

EMU | |||||||||||||||||||||||||

Static | |||||||||||||||||||||||||

| Static | ||||||||||||||||||||||||

SetupInput (Min) | HoldInput (Min) | OutputValid (Max) | OutputHold (Min) | OutputEnable (Min) | OutputDisable | (Max) | Reference Clock |

|

|

|

| 1 | 1 |

| |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.0 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 3.6 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.2 | 0.9 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | — | — | — | — |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | — | — | — | — |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | — | — |

| SCLK |

— | — | 4.0 | 1.0 | — | — |

| SCLK |

— | — | 4.0 | 1.0 | 1.0 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 0.75 | 2.0 |

| SCLK |

1.5 | 0.5 | 29.5 | 2.0 | 0.75 | 2.0 |

| SCLK |

1.5 | 0.5 | 4.0 | 1.0 | 0.75 | 2.0 |

| SCLK |

1.5 | 0.5 | 29.5 | 2.0 | 0.75 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

— | — | 4.0 | 1.0 | 1.15 | 2.0 |

| SCLK |

1.5 | 2.5 | — | — | — | — |

| SCLK5 |

1.5 | 0.5 | — | — | — | — |

| TCK |

1.5 | 0.5 | — | — | — | — |

| TCK |

— | — | 4.0 | 1.0 | 0.75 | 2.0 |

| TCK6 |

1.5 | 0.5 | — | — | — | — |

| TCK |

— | — | 5.5 | 2.0 | 1.15 | 4.0 |

| TCK or SCLK |

— | — | — | — | — | — |

| — |

— | — | — | — | — | — |

| — |

|

|

|

|

|

|

|

|

Rev. C Page 28 of 48 December 2006