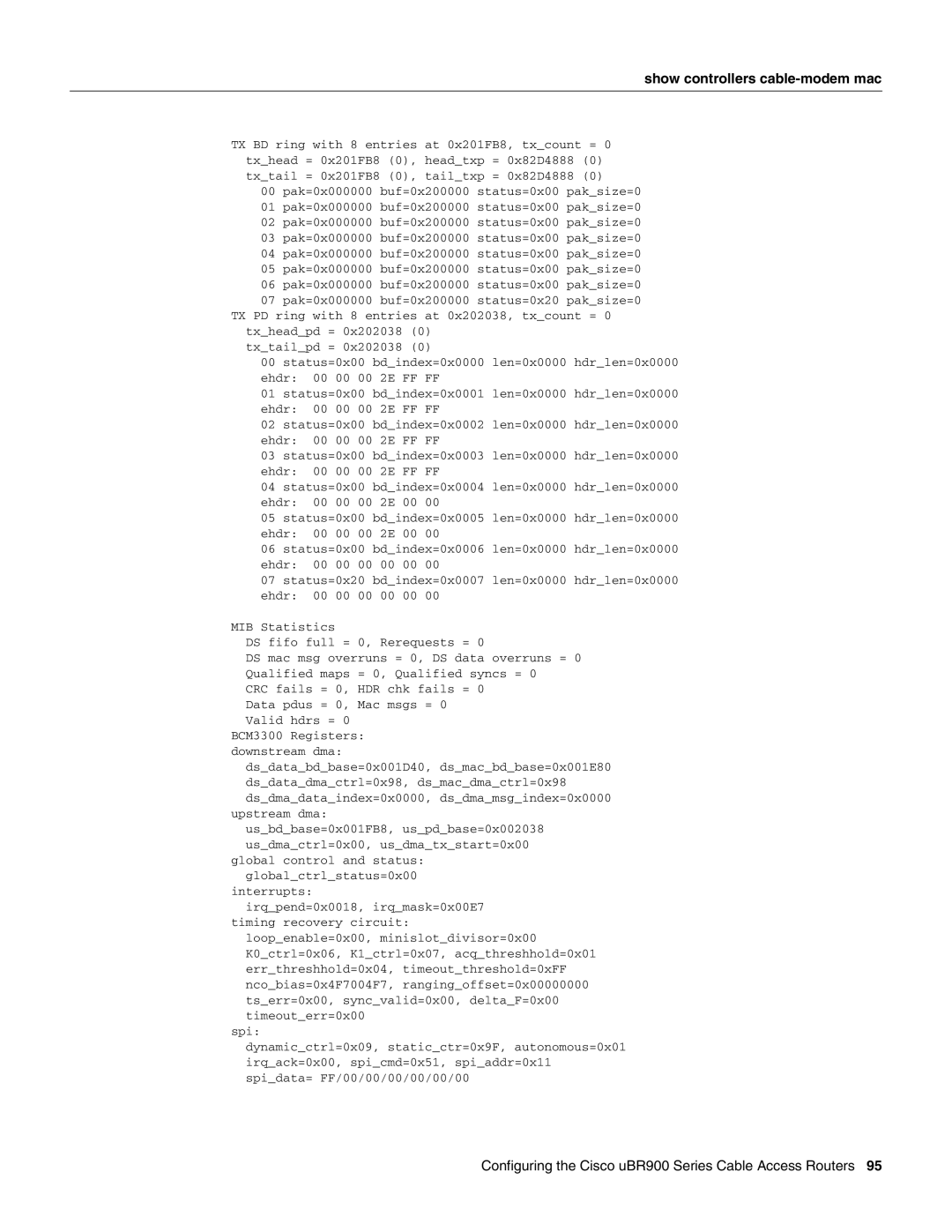

show controllers cable-modem mac

TX BD ring with 8 entries at 0x201FB8, tx_count = 0 tx_head = 0x201FB8 (0), head_txp = 0x82D4888 (0) tx_tail = 0x201FB8 (0), tail_txp = 0x82D4888 (0)

00pak=0x000000 buf=0x200000 status=0x00 pak_size=0

01pak=0x000000 buf=0x200000 status=0x00 pak_size=0

02pak=0x000000 buf=0x200000 status=0x00 pak_size=0

03pak=0x000000 buf=0x200000 status=0x00 pak_size=0

04pak=0x000000 buf=0x200000 status=0x00 pak_size=0

05pak=0x000000 buf=0x200000 status=0x00 pak_size=0

06pak=0x000000 buf=0x200000 status=0x00 pak_size=0

07pak=0x000000 buf=0x200000 status=0x20 pak_size=0

TX PD ring with 8 entries at 0x202038, tx_count = 0 tx_head_pd = 0x202038 (0)

tx_tail_pd = 0x202038 (0)

00status=0x00 bd_index=0x0000 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 2E FF FF

01status=0x00 bd_index=0x0001 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 2E FF FF

02status=0x00 bd_index=0x0002 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 2E FF FF

03status=0x00 bd_index=0x0003 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 2E FF FF

04status=0x00 bd_index=0x0004 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 2E 00 00

05status=0x00 bd_index=0x0005 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 2E 00 00

06status=0x00 bd_index=0x0006 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 00 00 00

07status=0x20 bd_index=0x0007 len=0x0000 hdr_len=0x0000 ehdr: 00 00 00 00 00 00

MIB Statistics

DS fifo full = 0, Rerequests = 0

DS mac msg overruns = 0, DS data overruns = 0 Qualified maps = 0, Qualified syncs = 0

CRC fails = 0, HDR chk fails = 0 Data pdus = 0, Mac msgs = 0 Valid hdrs = 0

BCM3300 Registers: downstream dma:

ds_data_bd_base=0x001D40, ds_mac_bd_base=0x001E80 ds_data_dma_ctrl=0x98, ds_mac_dma_ctrl=0x98 ds_dma_data_index=0x0000, ds_dma_msg_index=0x0000

upstream dma:

us_bd_base=0x001FB8, us_pd_base=0x002038 us_dma_ctrl=0x00, us_dma_tx_start=0x00

global control and status: global_ctrl_status=0x00

interrupts:

irq_pend=0x0018, irq_mask=0x00E7 timing recovery circuit:

loop_enable=0x00, minislot_divisor=0x00

K0_ctrl=0x06, K1_ctrl=0x07, acq_threshhold=0x01 err_threshhold=0x04, timeout_threshold=0xFF nco_bias=0x4F7004F7, ranging_offset=0x00000000 ts_err=0x00, sync_valid=0x00, delta_F=0x00 timeout_err=0x00

spi:

dynamic_ctrl=0x09, static_ctr=0x9F, autonomous=0x01 irq_ack=0x00, spi_cmd=0x51, spi_addr=0x11 spi_data= FF/00/00/00/00/00/00

Configuring the Cisco uBR900 Series Cable Access Routers 95