|

|

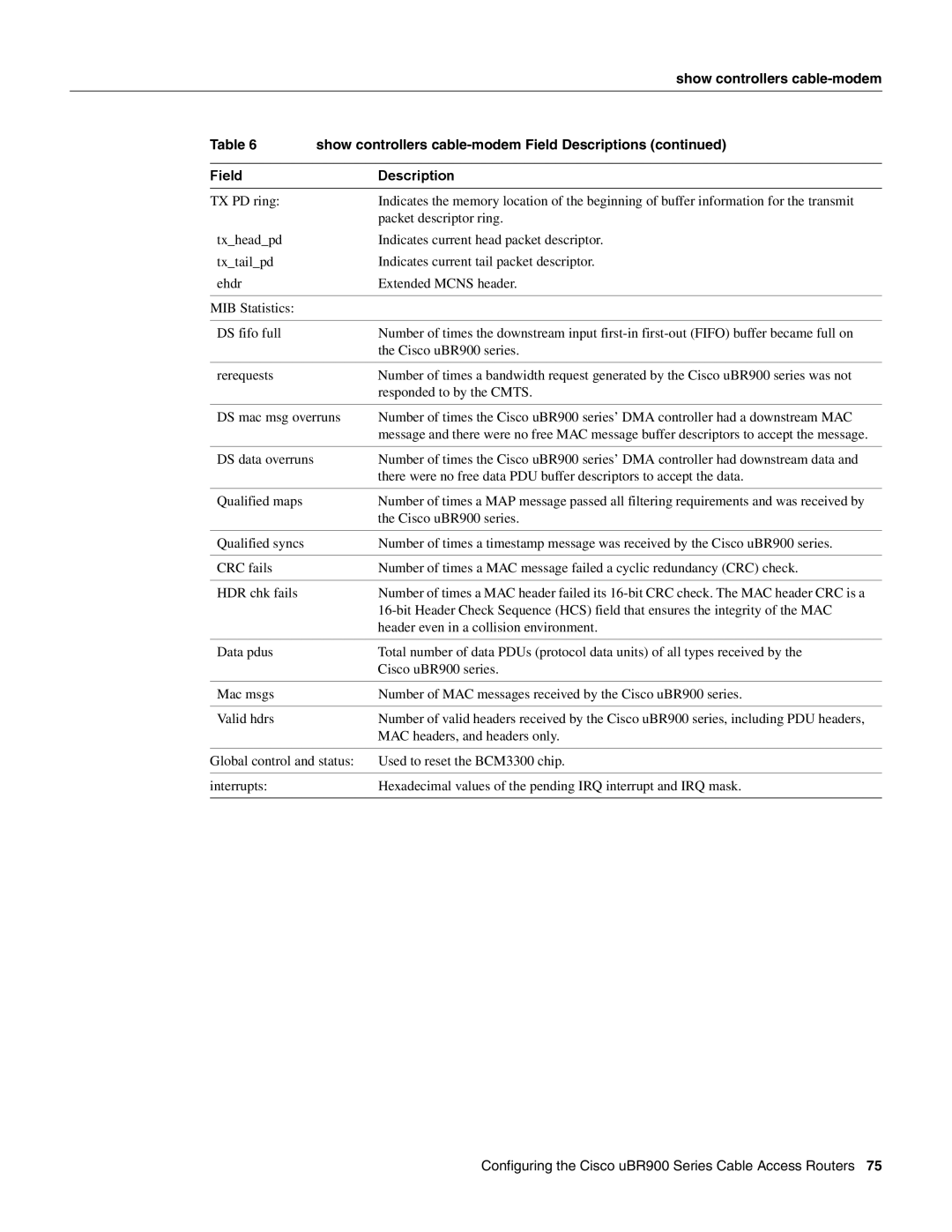

| show controllers |

| Table 6 | show controllers | |

|

|

|

|

| Field |

| Description |

|

|

|

|

| TX PD ring: |

| Indicates the memory location of the beginning of buffer information for the transmit |

|

|

| packet descriptor ring. |

| tx_head_pd |

| Indicates current head packet descriptor. |

| tx_tail_pd |

| Indicates current tail packet descriptor. |

| ehdr |

| Extended MCNS header. |

|

|

|

|

| MIB Statistics: |

|

|

|

|

|

|

| DS fifo full |

| Number of times the downstream input |

|

|

| the Cisco uBR900 series. |

|

|

|

|

| rerequests |

| Number of times a bandwidth request generated by the Cisco uBR900 series was not |

|

|

| responded to by the CMTS. |

|

|

| |

| DS mac msg overruns | Number of times the Cisco uBR900 series’ DMA controller had a downstream MAC | |

|

|

| message and there were no free MAC message buffer descriptors to accept the message. |

|

|

|

|

| DS data overruns |

| Number of times the Cisco uBR900 series’ DMA controller had downstream data and |

|

|

| there were no free data PDU buffer descriptors to accept the data. |

|

|

|

|

| Qualified maps |

| Number of times a MAP message passed all filtering requirements and was received by |

|

|

| the Cisco uBR900 series. |

|

|

|

|

| Qualified syncs |

| Number of times a timestamp message was received by the Cisco uBR900 series. |

|

|

|

|

| CRC fails |

| Number of times a MAC message failed a cyclic redundancy (CRC) check. |

|

|

|

|

| HDR chk fails |

| Number of times a MAC header failed its |

|

|

| |

|

|

| header even in a collision environment. |

|

|

|

|

| Data pdus |

| Total number of data PDUs (protocol data units) of all types received by the |

|

|

| Cisco uBR900 series. |

|

|

|

|

| Mac msgs |

| Number of MAC messages received by the Cisco uBR900 series. |

|

|

|

|

| Valid hdrs |

| Number of valid headers received by the Cisco uBR900 series, including PDU headers, |

|

|

| MAC headers, and headers only. |

|

|

| |

| Global control and status: | Used to reset the BCM3300 chip. | |

|

|

|

|

| interrupts: |

| Hexadecimal values of the pending IRQ interrupt and IRQ mask. |

|

|

|

|

Configuring the Cisco uBR900 Series Cable Access Routers 75