Page

Page

Page

Preface

PLEASE READ PRIOR TO INSTALLATION FOR SAFETY

DANGER

Page

Chapter 2 Installation and Wiring

Table of Contents

Table of Contents

Preface

Chapter 4 Digital Keypad Operation

Chapter 5 Parameters

Chapter 6 Fault Code Information

Chapter 7 Troubleshooting

Appendix B Accessories

Chapter 8 Maintenance and Inspections

Appendix A Specifications

Appendix C How to Select the Right AC Motor Drive

1.1.1 Nameplate Information

Chapter 1 Introduction

1.1 Receiving and Inspection

1.1.2 Model Explanation

1.2 Appearances

1.1.3 Series Number Explanation

1.1.4 Drive Frames

Taoyuan 230V 3-phase 1HP0.75kW Model

1.3 Installation Steps

1.4 Storage

3. If the AC motor drive is stored for more than 3 months, the temperature should not be higher than 30 C. Storage longer than one year is not recommended, it could result in the degradation of the electrolytic capacitors

This page intentionally left blank

Chapter 2 Installation and Wiring

2.2 Installation

2.1 Ambient Conditions

150mm 6inch

Air Flow

50mm 2inch 50mm 2inch 150mm 6inch

2.3 Dimensions

Dimensions are in millimeter and inch

Frame S1 VFD002S11A, VFD002S21A, VFD002S23A

13 .0 0 .5

5. 8 0

88 .0 3 .4

73 .0 2 .8

2 .9

3 .3

5. 8 0

5. 0 0

74 .0 2 .9

85 .0 3 .3

10 2. 0 4

2. 8

2.25.21

85 .0 3 .3 74 .0 2 .9

12 4. 0 4 2. 8 0 5. 0 0

8.05.83

2 .9

3 .3

12 4. 0 4

2. 8 0

12 6. 0 4 3. 0 0 5. 0 0

13 2.2 5.21 14 8.0 3.0 0

67 .8 2 .6

12 6. 0 4

3. 0 0

51 .0 2 .0

12 7. 0 5

3 .3

5. 8 0

2 .9

12 9. 0 5

86 .5 3 .4

5. 4 0

5. 5 0

9.50.38

10 0. 0 3 86 .5 3 .4 73 .0 2 .8

6.82

5. 4 0

12 9. 3 5 8. 5 0

5. 4 0

5. 5 0

86 .5 3 .4

53.9

Frame S2 VFD015S21U, VFD015S43U, VFD022S21U, VFD022S43U

67.8

6.50.26

2.4 Wiring

2.4.1 Basic Wiring

Basic Wiring Diagrams

For VFDXXXSXXA/B/D/U

when power supply

fault output

Recommended Circuit

S/L2

Chapter 2 Installation and WiringVFD-S Series

R/L1

T/L3

Two/Three wire control

For VFDXXXSXXE

NPN Mode

PNP Mode

2.4.2 External Wiring

Control circuit terminals U/T1, V/T2, W/T3

2.4.3 Main Terminals Connections

Mains power terminals R/L1, S/L2, T/L3 and L/L1, N/L2

Forward running

Terminals +2/B1, +1 for connecting DC reactor

Terminals +2/B1, B2 for connecting brake resistor

Grounding terminals

2.4.4 Control Terminals

RJ11

Control signal wiring size 18 AWG 0.75 mm2 with shielded wire

AFM circuit

Internal Circuit

Digital inputs M0~M5, GND

wind each wires 3 times or more around the core

Analog input terminals AVI, GND

Digital outputs MO1, MCM

2-28

Power terminal

2.4.5 Main Circuit Terminals

AC Input Line

Motor

2-29

AC Input Line

Terminal

2-30

Groun d Brake DC Reactor Resistor

Groun d

Power terminal

2-31

Brake Resistor

2-32

Groun d Brake DC Reacto r Resistor

2-33

Br ake DC Reacto r

Resistor

2-34

The keypad should light up as follows normal status with no error

Chapter 3 Start Up

3.1 Preparations before Start-up

If the drive has built-in fan, it should run

„ Check if the motor direction of rotation is correct

3.2 Operation Method

3.3 Trial Run

„ Check if acceleration and deceleration are smooth

1. Stop running immediately if any fault occurs and refer to the troubleshooting guide for solving the problem

This page intentionally left blank

4.1 Description of the Digital Keypad

4.2 Explanation of LED Indicators

Chapter 4 Digital Keypad Operation

4.3 Explanations of Display Messages

The internal PLC process step currently being performed

4.4 How to Operate the Digital Keypad

To shift data

This page intentionally left blank

Chapter 5 Parameters

5.1 Summary of Parameter Settings

Chapter 5 ParametersVFD-S Series

Setting

Group 2 Operation Method Parameters

Explanation

Group 3 Output Function Parameters

Explanation

Group 5 Multi-Step Speed and PLC Parameters

Explanation

Settings

Setting

Factory

Explanation

Group 9 Communication Parameters

Explanation

5.2 Parameter Settings for Applications

„ Two-wire/three-wire

„ Over-torque Setting

„ Output Signal during Running

„ Output Signal when Frequency Attained

0-00

5.3 Description of Parameter Settings

This parameter can be set during operation

0-01

d2 Multifunction display, see Pr.0-04 d3 Display output current LED A

0-04

0-05

0-06

0-07

0-08

0-07

Password Decode Flow Chart

0-08

0-09

Chapter 5 Parameters VFD-S Series

Setting for Pr

8 factory setting

5-21

1-02

1-00

1-01

1-03

Standard V/F Curve

1-05

1-06

1-07

1-11

1-09

1-10

1-12

Time

Acceleration Time Jog operation commandON

Frequency

Max. output Freq. Pr.1-00

Acceleration/deceleration Characteristics

Disable S curve

Enable S curve

1-18

J1 Voltage signal input0-10V Current signal input4-20mA

2-01 Source of Operation Command

2-02

3kHz

10kHz

115V/230V/460V Series

2-05 Loss of ACI Signal 4-20mA

3-01

Analog Frequency Meter

Analog Current Meter

Freq

3-06

Counter Trigger Signal Multi-function Input Terminal

2ms 2ms The width of trigger signal should not be less than 2ms250 Hz

Display Pr.0-04=d1 TRG

Setting

4-02

4-00

4-01

4-03

This example shows a potentiometer range of 0 to 5 Volts

0 Hz

Potentiometer Scale

Max Output Pr.1-00 Freq 60Hz

Potentiometer Scale

4-08

4-06

4-07

Parameters & Functions table

RUN/STOP

FWD/STOP

REV/STOP

REV/FWD

d4, d5 External Faults

setting by d5 GND

RESET Mx Close Operation available setting by d6 GND

d6 External Reset

Mx Close Operation available d10 jog operation command GND

d10 Jog Operation Control

d11 Acceleration/Deceleration Speed Inhibit

d12 First or Second Acceleration/Deceleration Time Selection

d13, d14 External Base Block

Chapter 5 ParametersVFD-S Series

UP setting by d15 DOWN setting by d16

B.B.N.O Mx Close Operation available. setting by d13 B.B.N.C

Mx OpenOperation available. setting by d14 GND

Mx Close Freq. will increase by one unit

PLC operation Mx Close Run PLC. setting by d17 Mx ClosePause PLC

setting by d18 GND

d19 Counter Trigger

d22 PID function disable

Reset counter Mx close reset counter d20 reset the counter value GND

d20 Counter Reset

d27 Press UP/DOWN key to switch forward/reverse N.O. motion

4-11

RUN/STOP

M0 Open Stop, Close Run M1 No Function GND

5-02

5-00

5-01

5-03

Example 2 Pr.5-07 = d2 Continuously executes program cycles

Example 3 Pr. 5-07 = d3 Execute one cycle step by step

Example 4 Pr. 5-07 =d4 Continuously execute PLC cycles step by step

5-08

Weights

Example 5 Pr. 5-07 = d1 Execute one cycle of the PLC program

0=Forward

5-11

5-09

5-10

5-12

6-01

Over-voltage Stall Prevention

Over-current Stall Prevention Level

6-05

6-03 Over-Torque Detection Mode OL2

6-04

6-07

Third Most Recent Fault Record

Present Fault Record

Second Most Recent Fault Record

6-08

d20 Software protection enable codE d21 Reserved

7-02

7-00

7-01

7-03

8-01

Output Frequency

8-00

8-02

8-06

8-04 Momentary Power Loss Operation Selection

8-05

8-07

8-11

8-08 Skip Frequency 1 Upper Limit

8-10

8-12

8-16

8-15

Automatic Voltage Regulation AVR

8-17

9-01

RS485

Computer

9-03

1 +EV 2 GND 3 SG- 4 SG+

7.N.2

ASCII mode

RTU mode

7.E.1

ASCII mode

3.2 ADR Communication Address

RTU mode Command message

3 Command code 10H, write n word, n=12

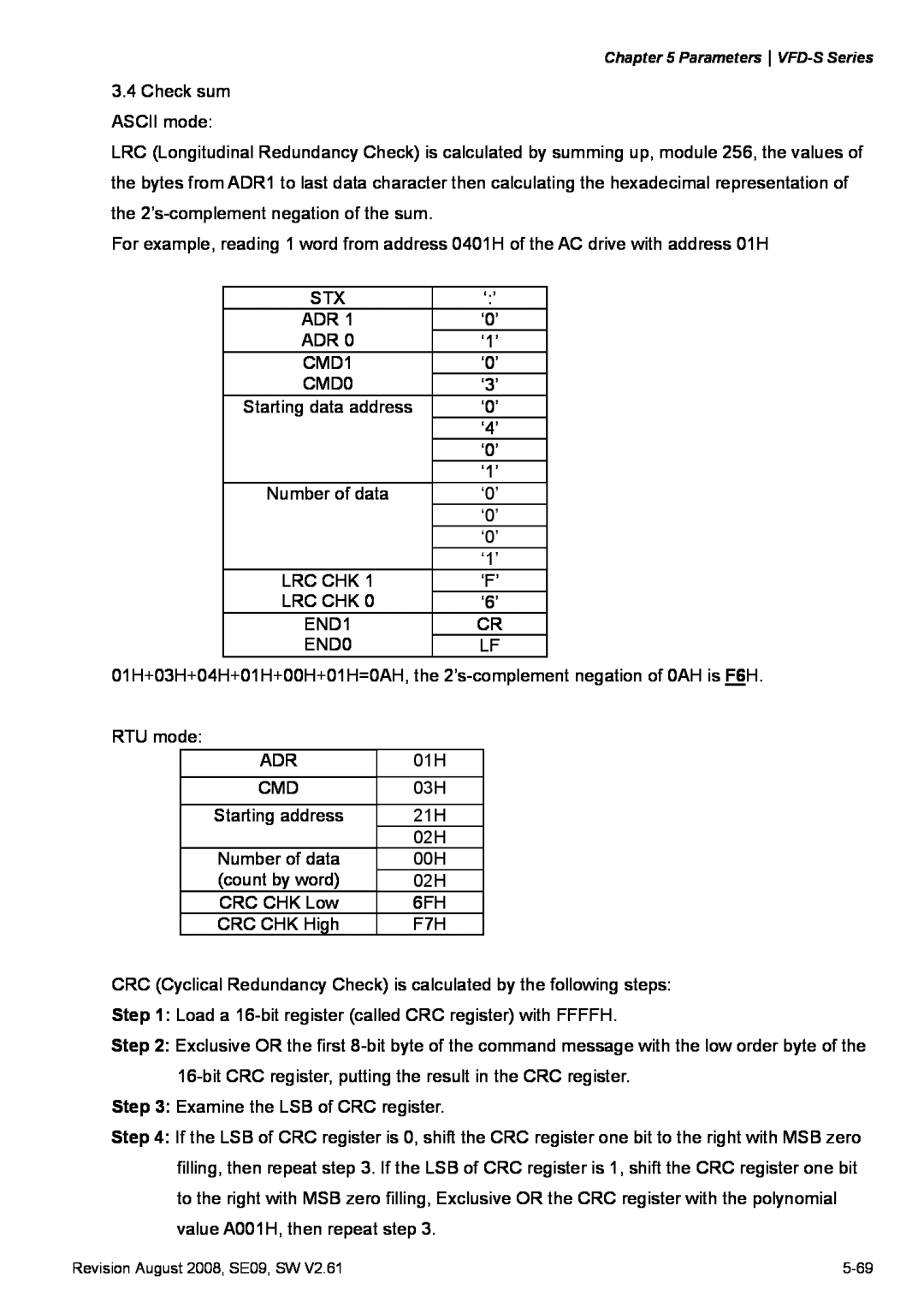

3.4 Check sum ASCII mode

Unsigned char* data Å a pointer to the message buffer

Content

Address

Functions

Content

Meaning

Error message

Exception

code

3.7 Communication program of PC

A-02

A-00

A-01

A-03

A-07

A-05

A-06

A-08

A-11

Sleep Function

A-10

A-12

Drange

+ + +

1-00

A-13 = 56-0 X 100100 X 10 =

Chapter 6 Fault Code Information

6.1 Common Problems and Solutions

Chapter 6 Fault Code InformationVFD-S Series

Fault

6.2 Reset

Over-current during acceleration

Chapter 7 Troubleshooting

7.1 Over Current OC

Over-current during deceleration

Ground fault

7.2 Ground Fault

7.3 Over Voltage OV

Chapter 7 Troubleshooting VFD-S Series

7.4 Low Voltage Lv

Check for correct settings at

7.5 Over Heat OH

7.6 Overload

OL1/ OL2

Check if all connectors are connect correctly and no noise is present

7.8 Phase Loss PHL

7.7 Keypad Display is Abnormal

Check wiring at R, S and T terminals

7.9 Motor cannot Run

out of range upper/lower

7.10 Motor Speed cannot be Changed

Check to see if frequency is

boundaries

settings

7.11 Motor Stalls during Acceleration

7.12 The Motor does not Run as Expected

Check if the inertia

7.13 Electromagnetic/Induction Noise

7.14 Environmental Condition

7.15 Affecting Other Machines

Chapter 8 Maintenance and Inspections

Daily Inspection

Periodic Inspection

Chapter 8 Maintenance and InspectionsVFD-S Series

Maintenance

„ DC capacity of main circuit

„ Printed circuit board and connector of main circuit

Chapter 8 Maintenance and InspectionsVFD-S Series

115V Class

Appendix A Specifications

Voltage Class

230V Class

Voltage Class

Appendix A SpecificationsVFD-S Series

General Specifications

460V Class

Appendix B Accessories

B.1 All Brake Resistors & Brake Units Used in AC Motor Drives

9. Definition for Brake Usage ED%

B.1.1 Dimensions and Weights for Brake resistors

General precaution

B.2 EMI Filters

Installation

Choose suitable motor cable and precautions

1. Use the cable with shielding double shielding is the best

The length of motor cable

B.2.1 Dimensions

Order P/N RF007S21AA/ RF007S43AA

Order P/N RF022S21BA

POWER-IN

Order P/N 12DKT1W3S

Order P/N 08TDT1W4S

B-10

B.3 AC Reactor B.3.1 AC Input Reactor Recommended Value

B.3.2 AC Output Reactor Recommended Value

B.3.3 Applications for AC Reactor

Application

B.4 DC Choke Recommended Values

Power

B.5 Zero Phase Reactor RF220X00A

Zero Phase Reactor

Supply

B.6 Din Rail-DR01

Models

Screw Size

VFD-S Programming Pr. 2-00 set to d01 Pr. 2-01 set to d01

B.7 Remote Controller RC-01

Pr. 4-05 set to d06 M2 set for reset

Pr. 4-04 set to d02 M0, M1 set at RUN/STOP and FWD/REV

B.8 Conduit Bracket BK-S

73.02.87

B-18

B.9 Non-fuse Circuit Breaker Chart

Fuse Specification Chart

B-20

Appendix C How to Select the Right AC Motor Drive

Related Specification

n T + I M ⎢1+

C.1 Capacity Formulas

n T + n s k s − 1 = P C 1 ⎢ ⎢

k ⋅ N

k ⋅ 3 ⋅VM ⋅ IM ⋅10−3 ≤ the capacity of AC motor drivekVA

Symbol explanation

k ⋅ IM ≤ the rated current of AC motor drive A

cosϕ

C.2 General Precautions

Parameter Settings Note

Selection Note

25% 40% 60% 100

C.3 How to Choose a Suitable Motor

torque%

continuous

„ To avoid resonances, use the Skip frequencies

Special motors

Power Transmission Mechanism

Motor torque

Motor