Concepts

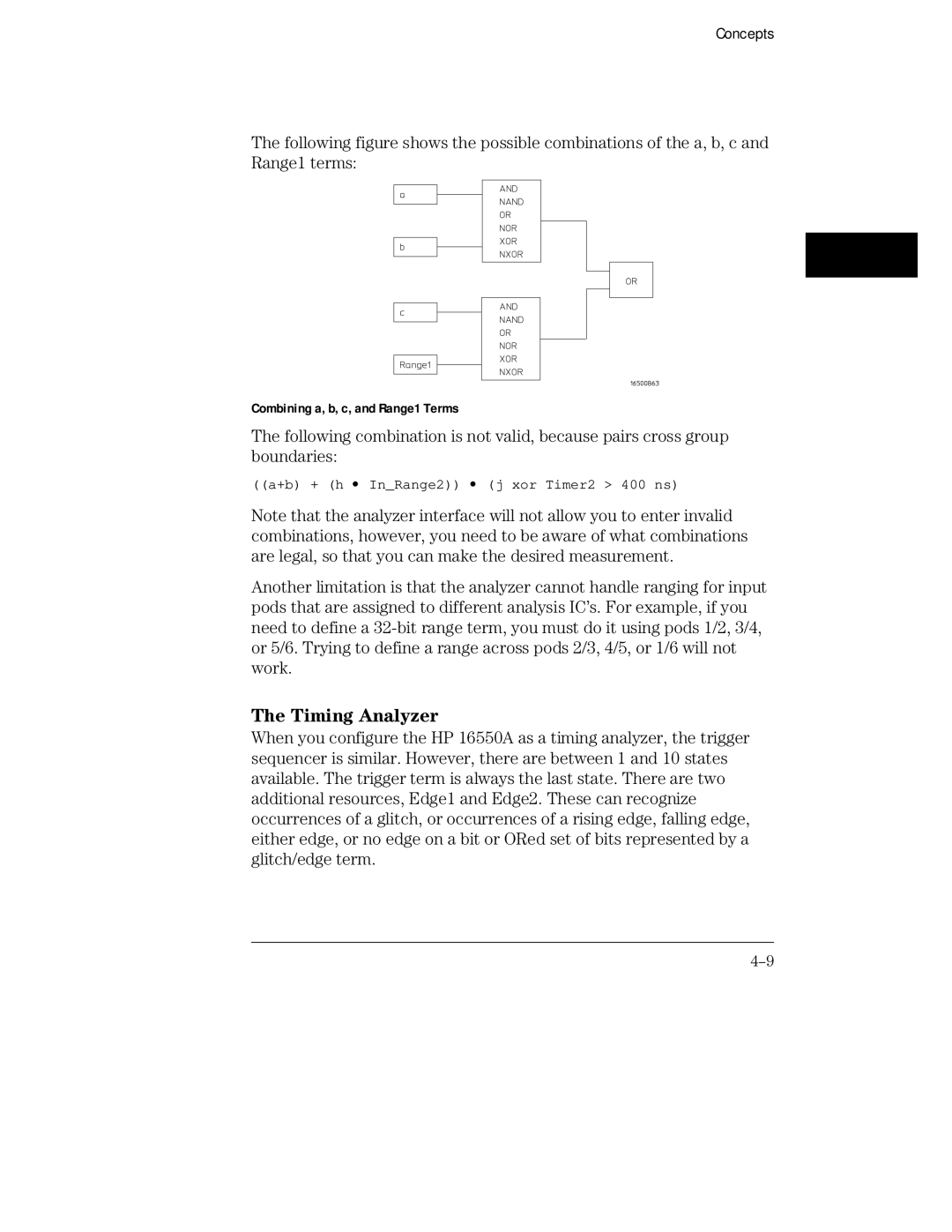

The following figure shows the possible combinations of the a, b, c and Range1 terms:

Combining a, b, c, and Range1 Terms

The following combination is not valid, because pairs cross group boundaries:

((a+b) + (h ∙ In_Range2)) ∙ (j xor Timer2 > 400 ns)

Note that the analyzer interface will not allow you to enter invalid combinations, however, you need to be aware of what combinations are legal, so that you can make the desired measurement.

Another limitation is that the analyzer cannot handle ranging for input pods that are assigned to different analysis IC’s. For example, if you need to define a

The Timing Analyzer

When you configure the HP 16550A as a timing analyzer, the trigger sequencer is similar. However, there are between 1 and 10 states available. The trigger term is always the last state. There are two additional resources, Edge1 and Edge2. These can recognize occurrences of a glitch, or occurrences of a rising edge, falling edge, either edge, or no edge on a bit or ORed set of bits represented by a glitch/edge term.