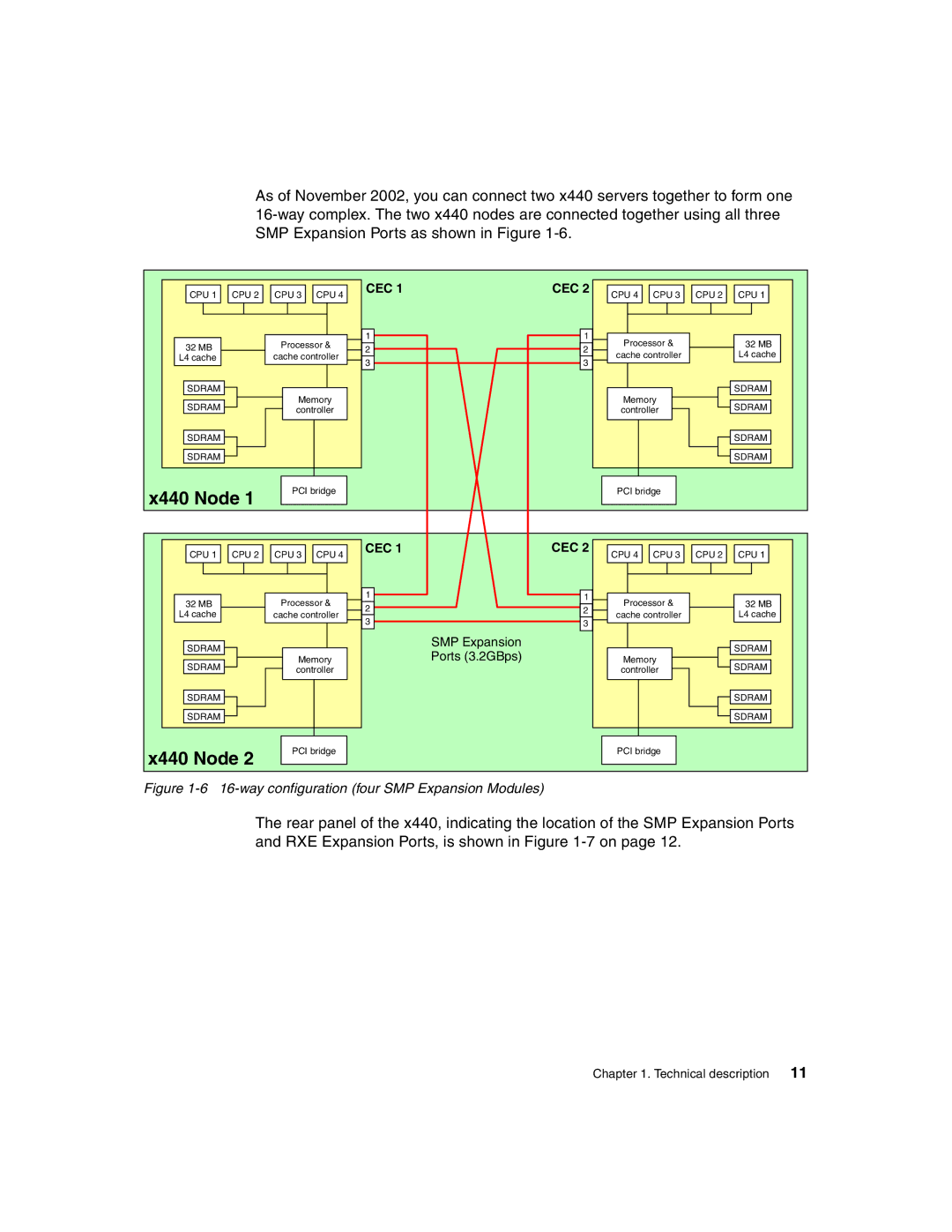

As of November 2002, you can connect two x440 servers together to form one

CPU 1 CPU 2 CPU 3 CPU 4 |

CEC 1 | CEC 2 | ||

|

|

|

|

1 |

| 1 | |

CPU 4 ![]()

![]() CPU 3

CPU 3 ![]()

![]() CPU 2

CPU 2 ![]()

![]() CPU 1

CPU 1

|

| 32 MB |

|

|

|

| Processor & | ||||

| L4 cache |

|

| cache controller |

| ||||||

|

|

|

|

|

|

|

|

|

| ||

|

| SDRAM |

|

|

|

|

|

|

| ||

|

|

|

|

| Memory |

| |||||

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| ||||

|

| SDRAM |

|

|

| controller |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SDRAM |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| SDRAM |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 | 2 |

3 | 3 |

Processor &

cache controller

Memory

controller

32 MB

L4 cache

![]() SDRAM

SDRAM

![]() SDRAM

SDRAM

![]() SDRAM

SDRAM

![]() SDRAM

SDRAM

x440 Node 1 | PCI bridge |

|

PCI bridge

CPU 1 CPU 2 CPU 3 CPU 4 |

CEC 1 | CEC 2 | ||

|

|

|

|

1 |

|

|

|

| 1 | ||

CPU 4 ![]()

![]() CPU 3

CPU 3 ![]()

![]() CPU 2

CPU 2 ![]()

![]() CPU 1

CPU 1

|

| 32 MB |

|

|

|

| Processor & | ||||

| L4 cache |

| cache controller | ||||||||

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| ||

|

| SDRAM |

|

|

|

|

|

|

| ||

|

|

|

|

| Memory |

| |||||

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| ||||

|

| SDRAM |

|

|

| controller |

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| SDRAM |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| SDRAM |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 | 2 | ||

3 |

|

| 3 |

|

| ||

SMP Expansion

Ports (3.2GBps)

Processor &

cache controller

Memory

controller

32 MB

L4 cache

![]() SDRAM

SDRAM

![]() SDRAM

SDRAM

![]() SDRAM

SDRAM

![]() SDRAM

SDRAM

x440 Node 2 | PCI bridge |

|

PCI bridge

Figure 1-6 16-way configuration (four SMP Expansion Modules)

The rear panel of the x440, indicating the location of the SMP Expansion Ports and RXE Expansion Ports, is shown in Figure

Chapter 1. Technical description | 11 |