88F6281

Hardware Specifications

Doc Status Preliminary Technical Publication

88F6281 Hardware Specifications

Document Conventions Document Status

Integrated Controller

Hardware Specifications

88F6281

High-performance CPU core, running at up to

Features

Supports Ieee 802.1Qav draft Audio Video Bridging networks

Features

Bit/4-bit SDmem, SDIO, and MMC cards Up to 50 MHz

GbE Port 0 in Gmii mode or GbE Port

TDM

X16

Table of Contents

129

Table of Contents

130

132

Clocking

List of Tables

List of Tables

Revision History 134

Hsbga 288-pin Package Dimensions 131

88F6281 Part Order Options 132

List of Figures

Pin and Signal Descriptions

Inter-IC Sound I2S Test Circuit 107

Preface

About this Document

Related Documentation

Following conventions are used in this document

Document Conventions

Pin and Signal Descriptions

Pin Logic

Power

Flash

Misc PCI Express

Pin Functions and Assignments Table Key

Pin Descriptions

Interface Pin Prefix Codes

Term Definition

RTC

88F6281 Hardware Specifications Interface Pin Prefix Codes

MPP Twsi Uart

SPI Sdio TDM PTP

Pin Name Description Type

Power Supply Pins

Power Pin Assignments

88F6281 Hardware Specifications Power Pin Assignments

Miscellaneous Pin Assignments

Pin Name Power Description Type Rail

Miscellaneous Pin Assignment

DDR Sdram Interface Pin Assignments

DDR Sdram Interface Pin Assignments

Mclkout Sstl Vddm

Mcke Sstl Vddm

Mstart Sstl Vddm

Mstartburst Sstl Vddm

Burstin Mpcal

Mncal

PCI Express Interface Pin Assignments

PCI Express Interface Pin Assignments

Sata Port Interface Pin Assignment

Pin Name Power Rail Description Type

Sata Interface Pin Assignments

Gigabit Ethernet Port0/1 Interface Pin Assignments

Pin Name Type Power Rail Description

Gigabit Ethernet Port Interface Pin Assignments

Cmos Vddgeb

Gerxctl Cmos Vddgea

Gerxclk Cmos Vddgea

MPP2724

Gmii Receive Error

MII/MMII Collision Detect

To any clock

Gmii Transmit Error

MII/MMII Transmit Error

MII/MMII Receive Error

MPP32/GE112

Serial Management Interface SMI Pin Assignments

Serial Management Interface SMI Interface Pin Assignments

Gemdc Cmos Vddgea

Gemdio Cmos Vddgea

USB 2.0 Data Differential Pair

USB 2.0 Interface Pin Assignments

USB 2.0 Interface Pin Assignments

Jtag Pin Assignment

Jtag Interface Pin Assignment

RTC Interface Pin Assignments

Real Time Clock RTC Interface Pin Assignments

Rtcxin

Rtcxout

Nand Flash Interface Pin Assignment

Nand Flash Interface Pin Assignment

Nfcle Cmos Vddo

Nfale Cmos Vddo

MPP Interface Pin Assignment

MPP Interface Pin Assignment

Two-Wire Serial Interface Twsi Interface Pin Assignment

Two-Wire Serial Interface Twsi Interface

Twsda Cmos Vddo

Twsck Cmos Vddo

Uart Port 0/1 Interface Pin Assignment

Uart Interface

Audio S/PDIF / I2S Interface

Audio S/PDIF / I2S Interface Signal Assignment

Multiplexing option

Fs is the audio sample rate

Pin Name Pin Type Power Rail Description

Serial Peripheral Interface SPI Interface Signal Assignment

Serial Peripheral Interface SPI Interface

SPICSn

Sdcmd Cmos Vddo

Secure Digital Input/Output Sdio Interface

Sdclk Cmos Vddo

Time Division Multiplexing TDM Interface

Time Division Multiplexing TDM Interface Signal Assignment

Tdmspimiso Cmos Vddo

Tdmspimosi Cmos Vddo

Transport Stream TS Interface

Transport Stream TS Interface Signal Assignment

TSMP8 Cmos Vddo

TSMP7 Cmos Vddo

TSMP9 Cmos Vddo

Cmos Vddo TS0DATA6 Vddgeb

Precise Timing Protocol PTP Interface

Precise Timing Protocol PTP Interface Signal Assignment

Ptpclk Cmos Vddo

Ptpeventreq Cmos Vddo

Pin Name Pin Number Pull up/Pull down

Internal Pull-up and Pull-down Pins

Internal Pull-up and Pull-down Pins

Unused Interface Strapping

Unused Interface Strapping

Unused Interface Strapping

88F6281 pin list is provided as an Excel file attachment

88F6281 Pin Map and Pin List

Pin Multiplexing

Multi-Purpose Pins Functional Summary

Pin Multiplexing

MPP190 MPP3520 MPP4936

MPP Functionality

Gpio

Sata LEDs Audio Nand flash GbE

Sysrsto Spimosi

MPP Function Summary

MPP Function Summary

TSMP0 Tdmspi Auspdifi

Configuration, on

Ethernet Ports Pins Multiplexing

Gigabit Ethernet GbE Pins Multiplexing on MPP

MPP34 MII1TXEN out GE114 MPP35 MII1RXERR GE115

TS Port Pin Multiplexing

Tsmp TS Multiplexing Pins on MPP

88F6281Clocks

Clocking

Lists the clocks in the 88F6281

Clock Type Description

Supported Clock Combinations

Clocking 88F6281Clocks

Sata PHY PLL

Ptpclk

Spread Spectrum Clock Generator Sscg

88F6192, and 88F6281 Functional Specifications

Power-Up/Down Sequence Requirements

System Power Up/Down and Reset Settings

Power-Up Sequence Requirements

System Power Up/Down and Reset Settings

88F6281

Hardware Reset

Power-Down Sequence Requirements

Power On Reset POR

Reset Out Signal

May reset all settings to the factory default values

SYSRSTn Duration Counter

Sheeva CPU TAP Controller Reset

PCI Express Reset

Pins Sample Configuration

PCI Express Root Complex Reset

Than the third Tclk cycle after SYSRSTn de-assertion

Reset Configuration

Pin Configuration Function

0x4 =

MPP33 Cpuclk to DDR CLK Ratio

0x0-0x3 = Reserved

= Enable

Sscg Disable

= Disable

PCI Express Clock 100 MHz Differential Clock Configuration

Pin Configuration Function MPP18 Reserved

88F6281 Hardware Specifications Reset Configuration

Serial ROM Initialization

Serial ROM Data Structure

Serial ROM Initialization Operation

Boot Sequence

88F6281 Hardware Specifications

TAP Controller

Jtag Interface

Instruction Register

Jtag Interface

Jtag Scan Chain

Bypass Register

ID Register

Idcode Register Map

Electrical Specifications Preliminary

Electrical Specifications Preliminary

Absolute Maximum Ratings

Absolute Maximum Ratings

125 Case temperature

88F6281 Hardware Specifications Absolute Maximum Ratings

125 Storage temperature

RTC interface

Recommended Operating Conditions

Recommended Operating Conditions

Parameter Min Typ Max Units Comments

MPP, TWSI, JTAG, SDIO, I 2S, SPI

Back-up mode

Analog supply for RTC in Battery

105 Junction Temperature

Internal clock inverter for crystal

Thermal Power Dissipation

Thermal Power Dissipation

Current Consumption

Interface Symbol Test Conditions Max Units

Current Consumption

CPU @ 1000 MHz

General 3.3V Cmos DC Electrical Specifications

DC Electrical Specifications

Electrical Specifications

General 3.3V Interface Cmos DC Electrical Specifications

35*VDDIO Input high level

Rgmii 1.8V Interface Cmos DC Electrical Specifications

VIH

65*VDDIO

RTT

Sdram DDR2 Interface DC Electrical Specifications

Sdram DDR2 Interface DC Electrical Specifications

SPI Interface 3.3V DC Electrical Specifications

Twsi Interface 3.3V DC Electrical Specifications

Following table, Vddio means the Vddo power rail

Following table Vddio means the Vddo power rail

TDM Interface 3.3V DC Electrical Specifications

Reference Clock AC Timing Specifications

AC Electrical Specifications

Reference Clock AC Timing Specifications

SMI Master Mode Reference Clock

Description Symbol Min Max Units Tdmspi Output Clock

Twsi Master Mode Reference Clock

Tclk

Sdram DDR2 Interface AC Timing

MHz @ Description Symbol Min Max

Sdram DDR2 Interface AC Timing Table

Sdram DDR2 Interface AC Timing Table

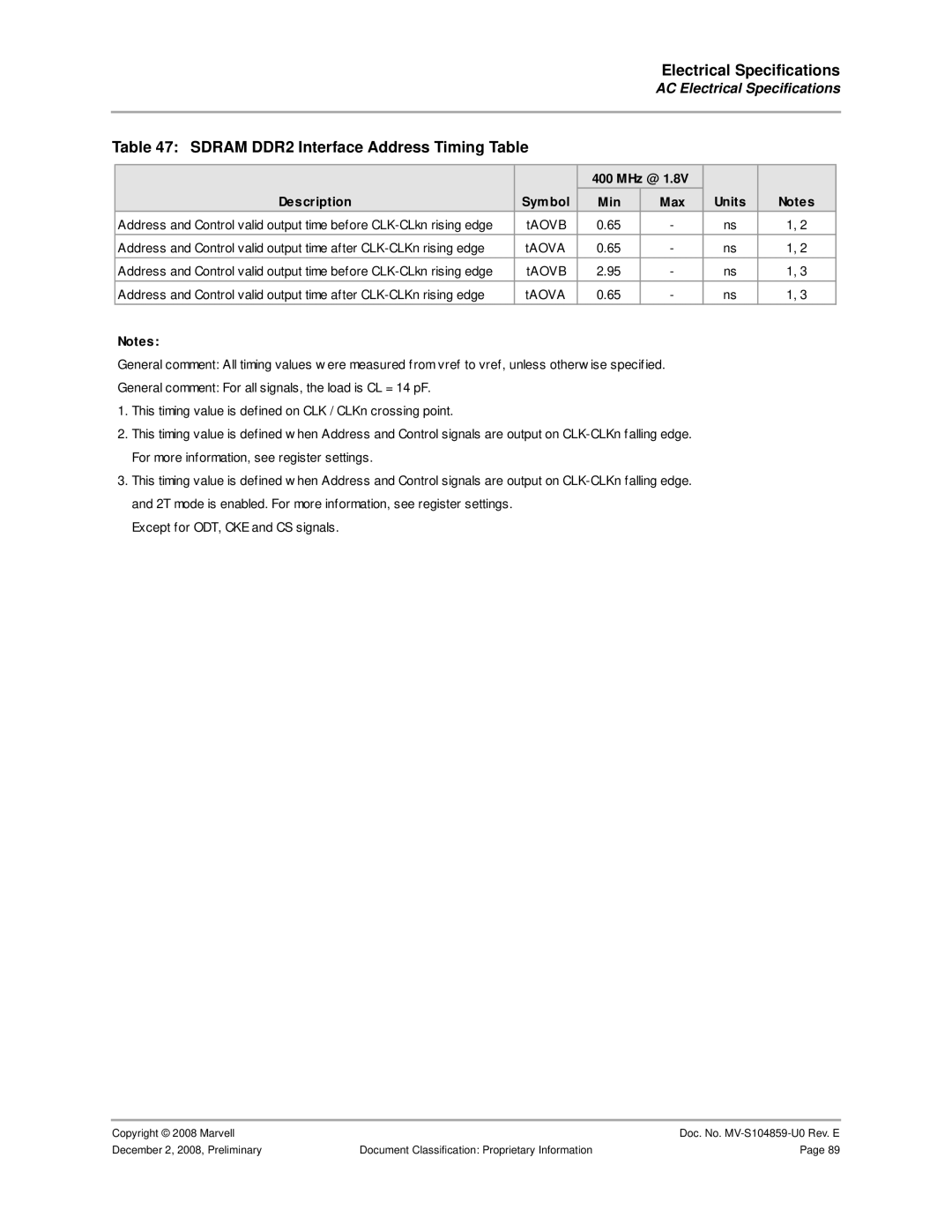

Sdram DDR2 Interface Address Timing Table

MHz @ Description Symbol Min Max Units

Description Symbol Min Max Units

Sdram DDR2 Clock Specifications

Sdram DDR2 Clock Specifications

Sdram DDR2 Interface Test Circuit

Sdram DDR2 Interface AC Timing Diagrams

VTT

CLK

DQSn TDSI tDHI

Address

Control

Rgmii AC Timing Table

Reduced Gigabit Media Independent Interface Rgmii AC Timing

Rgmii 10/100/1000 AC Timing Table at

Rgmii 10/100 AC Timing Table at

Rgmii Test Circuit

Rgmii AC Timing Diagram

Gigabit Media Independent Interface Gmii AC Timing

125 MHz Description Symbol Min Max

Gmii AC Timing Table

Gmii Test Circuit

TSETUP Hold

Gmii AC Timing Diagrams

VILmax

TLOW THIGH

5.2 MII/MMII MAC Mode Test Circuit

5.1 MII/MMII MAC Mode AC Timing Table

5.3 MII/MMII MAC Mode AC Timing Diagrams

MII/MMII MAC Mode AC Timing Table

MII/MMII MAC Mode Input AC Timing Diagram

SMI Master Mode Test Circuit

SMI Master Mode AC Timing Table

SMI Master Mode AC Timing Table

Serial Management Interface SMI AC Timing

MDC

SMI Master Mode AC Timing Diagrams

Jtag Interface AC Timing

30 MHz Description Symbol Min Max Units

Jtag Interface AC Timing Table

Jtag Interface Test Circuit

Jtag Interface Output Delay AC Timing Diagram

Jtag Interface AC Timing Diagrams

100 kHz Description Symbol

Two-Wire Serial Interface Twsi AC Timing

Twsi AC Timing Table

Twsi Master AC Timing Table

Twsi Test Circuit

Twsi AC Timing Diagrams

Pdif AC Timing Table

Sony/Philips Digital Interconnect Format S/PDIF AC Timing

9.1 S/PDIF AC Timing Table

Pdif Test Circuit

9.2 S/PDIF Test Circuit

Inter-IC Sound I2S AC Timing Table

Inter-IC Sound Interface I2S AC Timing

Inter-IC Sound I2S Test Circuit

Inter-IC Sound I2S AC Timing Table

Inter-IC Sound I2S Output Delay AC Timing Diagram

Inter-IC Sound I2S AC Timing Diagrams

Time Division Multiplexing TDM Interface AC Timing

192 MHz Description Symbol Min Max Units

TDM Interface AC Timing Table

TDM Interface Test Circuit

Pclk DRX

TDM Interface Timing Diagrams

Pclk DTX

SPI Master Mode Test Circuit

SPI Master Mode AC Timing Table

SPI Master Mode AC Timing Table

Description Symbol Min Max

TCH tCL

SPI Master Mode Timing Diagrams

Sclk

Data Out TDOVmin TDOVmax TCSB TCSA

Secure Digital Input/Output Sdio Interface AC Timing

Sdio Host in High Speed Mode AC Timing Table

Secure Digital Input/Output Sdio AC Timing Table

Secure Digital Input/Output Sdio Test Circuit

Sdio Host in High Speed Mode Output AC Timing Diagram

Secure Digital Input/Output Sdio AC Timing Diagrams

Transport Stream Interface AC Timing Table

Transport Stream TS Interface AC Timing

Transport Stream Output Interface AC Timing Table

Transport Stream Input Interface AC Timing Table

Transport Stream Interface Test Circuit

Transport Stream Interface Timing Diagrams

Transport Stream Input Interface AC Timing Diagram

Clock frequency FCK 100.0

Differential Interface Electrical Characteristics

Differential Interface Reference Clock Characteristics

Fmod 33.0

Symbol Min Max Units

PCI Express Interface Spread Spectrum Requirements

PCI Express Interface Driver and Receiver Characteristics

PCI Express Interface Electrical Characteristics

PCI Express Interface Driver and Receiver Characteristics

PCI Express Interface Test Circuit

PCI Express Interface Test Circuit

Sata Interface Electrical Characteristics

TJ5

Rlod

DJ5

Rlid

Differential return loss 3.0 GHz-5.0 GHz

Differential return loss 600 MHz-2.4 GHz

275.0 750.0 Differential return loss 150 MHz-300 MHz

18.0 Differential return loss 300 MHz-600 MHz

USB Driver and Receiver Characteristics

USB Electrical Characteristics

USB Low Speed Driver and Receiver Characteristics

Low Speed Description Sym bol Min Max Units

Min Max

Full Speed Description

USB Interface Driver Waveforms

USB High Speed Driver and Receiver Characteristics

High Speed Description Symbol Min Max

High Speed TX Eye Diagram Pattern Template

Thermal Data Preliminary

Symbol Definition Airflow Value C/W 0m/s 1m/s 2m/s

Thermal Data Preliminary

Package

Hsbga 288-pin Package and Dimensions

Symbol Common Dimension Millimeters

Package Hsbga 288-pin Package Dimensions

Package

Hsbga

Part Order Numbering

Part Order Numbering/Package Marking

88F6281 -xx-BIA2Cxxx-xxxx

88F6281 Part Order Options

Part Order Numbering/Package Marking

Package Marking

Revision Date Comments

Revision History

Revision History

, Power Pin Assignments, on

Revised , Reference Clock AC Timing Specifications, on

, Current Consumption, on page 80 added the following

January 28 Initial release

This page is Intentionally Left Blank

Page

Marvell. Moving Forward Faster