Contents

Circuit Card Manual

Page

Liability Disclaimer

Page

NEAX2400 IPX

Revision Sheet 2/9

Revision Sheet 3/9

Revision Sheet 4/9

Revision Sheet 5/9

Revision Sheet 6/9

Revision Sheet 7/9

Revision Sheet 8/9

Revision Sheet 9/9

Page

NEAX2400 IPX

Circuit Card Manual

Table of Contents

List of Figures

List of Figures

Location ofPA-CK14 OSC Card in the System

232

101 Connecting Route Diagram

121 Location ofPA-SDTA SDT Card in the System 433

161 Location ofPA-4DATB DAT within the System 531

NDA-24296LIST of Figures

List of Figures

List of Tables

Chapter

This page is for your notes

Introduction

NDA-24296CHAPTER

Mounting Location of Circuit Card

Card Mounting Slot for the 1 IMG System NDA-24296

Card Mounting Slot for the 4 IMG System 1/4

Card Mounting Slot for the 4 IMG System 2/4

Card Mounting Slot for the 4 IMG System 3/4

Card Mounting Slot for the 4 IMG System 4/4

Card Mounting Slot for the IPX-U System 1/5

Card Mounting Slot for the IPX-U System 2/5

Card Mounting Slot for the IPX-U System 3/5

Card Mounting Slot for the IPX-U System 4/5 NDA-24296

Card Mounting Slot for the IPX-U System 5/5

Card Mounting Slot for the IPX-UMG System 1/5 NDA-24296

Card Mounting Slot for the IPX-UMG System 2/5

Card Mounting Slot for the IPX-UMG System 3/5 NDA-24296

Card Mounting Slot for the IPX-UMG System 4/5

Card Mounting Slot for the IPX-UMG System 5/5

This page is for your notes

Control Circuit Card Reference

SN1695 CPRBF-A

CPU Board

SN1695 CPRBF-A

Operation. Note

CPR Location

SN1695 CPRBF-A in the IPX-UMG System

CPR Location for IPX-UMG System

Front View of CPR

CPR in SP for IPX-UMG System

CPR in LP for IPX-UMG System

Lamp Name Color Description

Status

Lamp SN1695 CPRBF-A

Description Name

DSP

Lamp Indications for the CPR in CMP

Lamp Indications for the CPR in LP

Lamp Description Name

Switch Name Setting Standard Meaning

Switch Setting Standard Meaning Name

Sense

SELECT0

DSP OFF

On the CPR of system #0 and #1

CMP

File copied from FDD to HD/Connection Hold Restart. Note

FDD/HDD MBR DSP System SELECT0

Switch Name Switch Shape Remarks

PWR

SELECT1 DSP System SELECT2 Sense

PH-GT09

Gate

PH-GT09

10 Face Layout of PH-GT09 GT NDA-24296

Lamp Name Color State

OPE/MB

Down

PH-GT10

Input Output Gate

PH-GT10

12 Location of PH-GT10 Iogt for IPX-UMG System

13 Face Layout

PH-GT10 Iogt

Pwralm

Lamp Name Color Meaning

OPE/MB OFF

CA4L

PA-PC94

Data Link Multiplexer

PA-PC94

PIM

OPE

ACT

Load OFF

MNT OFF

Switch Switch Shape Remarks Name

MNT Mode

Mode

Dual Power

PA-PW54-A

PA-PW54-A

PIM

17 Face Layout of PA-PW54-A Dpwr Card

Switch Setting Standard Description Name

Reset Down

SW4

PA-PW54-B

PA-PW54-B

Dpwr

19 Face Layout of PA-PW54-B Dpwr Card

Red Lights in the case of +5 V, +12 V, or -5 V outputs alarm

Circuit card make busy cancel

Power

PA-PW55-A

PA-PW55-A

PWR

21 Face Layout of PA-PW55-A Card

Switch Settings This circuit card has the following switches

Switch Setting Sheet

PA-PW55-B

PA-PW55-B

PWR NDA-24296CHAPTER

23 Face Layout of PA-PW55-B Card

Switch Settings This circuit card has the following switches

Switch Setting Sheet

PH-DK10

Display Panel Controller

PH-DK10

24 Location of PH-DK10 Dspc

25 Face Layout of PH-DK10 Dspc NDA-24296

Lamp Name Color State

26 Connection of Alarm Indicating Panel

Switch Name Switch Shape Remarks Chapter

PH-IO24

Input/Output Controller

PH-IO24

28 Face Layout of PH-IO24 IOC Card

IOC ALM

PORT0 PORT3

29 External Cable Connection for PH-IO24 IOC

Meaning of SW50-1

PH-M22

31 Location of PH-M22 MMC in IPX-UMG System NDA-24296

LPM/CMP/LP

Green Lights when this circuit card is in operation

33 Connection of Alarm Indicating Panel

Switch Name Switch Shape Remarks NDA-24296CHAPTER

PH-M16

Line Test

LPM

SW0

36 LT Connector Lead Accommodation

Switch Name Switch Shape Remarks

PH-PC36

Multiplexer

PH-PC36

38 Location of PH-PC36 MUX Card in the 4 IMG System

PH-PC36

40 PCM Highway Running

41 Face Layout of PH-PC36 MUX

Rclk ALM

MUX ACT

Sync

Pmclk ALM

42 External Interface for PH-PC36

43 Cable Connections between the MUX and the TSW

SW01

PH-PC20

Data Link Controller

PH-PC20

Switch Switch no Setting Standard Meaning Name

PWR ALM

No cable connections are required Switch Setting Sheet

Emergency Alarm Controller

PH-PC45

PH-PC45

47 Face Layout of the PH-PC45 EMA Card

ACT0

ACT1

Ckerr

Emsup

Topu OFF

PH-PC45

48 Connection of Alarm Indicating Panel and Music on Hold

EMA-SUP CPU-SEL NMI-SEL

SWA0

Power Switch

PH-PW14

PH-PW14

50 Face Layout of the PH-PW14 Card

Module Slot no Switch Switch Shape Remarks Name

ALM

Time Division Switch

PH-SW10

PH-SW10

52 PLO Function Diagram

53 Voice Prompting NDA-24296

54 Face Layout of PH-SW10 TSW

M3SY

Muxact

Ploact

M2SY

ECK

Sync OFF

ICK

Tswmbr

Party Conference Trunk CFT is valid

PLO operates as the clock subordinate office

55 PLO Connector Leads Location

56 Connecting Route Diagram

Front cable connections are shown in Figure

Tswmbr Plomb

PH-SW12

PH-SW12

Music/Tone Insertion

60 Speech Path Memory SPM for Voice Prompt Function

Symbol System Controlled IMG

Symbol System Function Controlled IMG

For the card in TSWM1

PLO

Tone

Tswmbr Tone

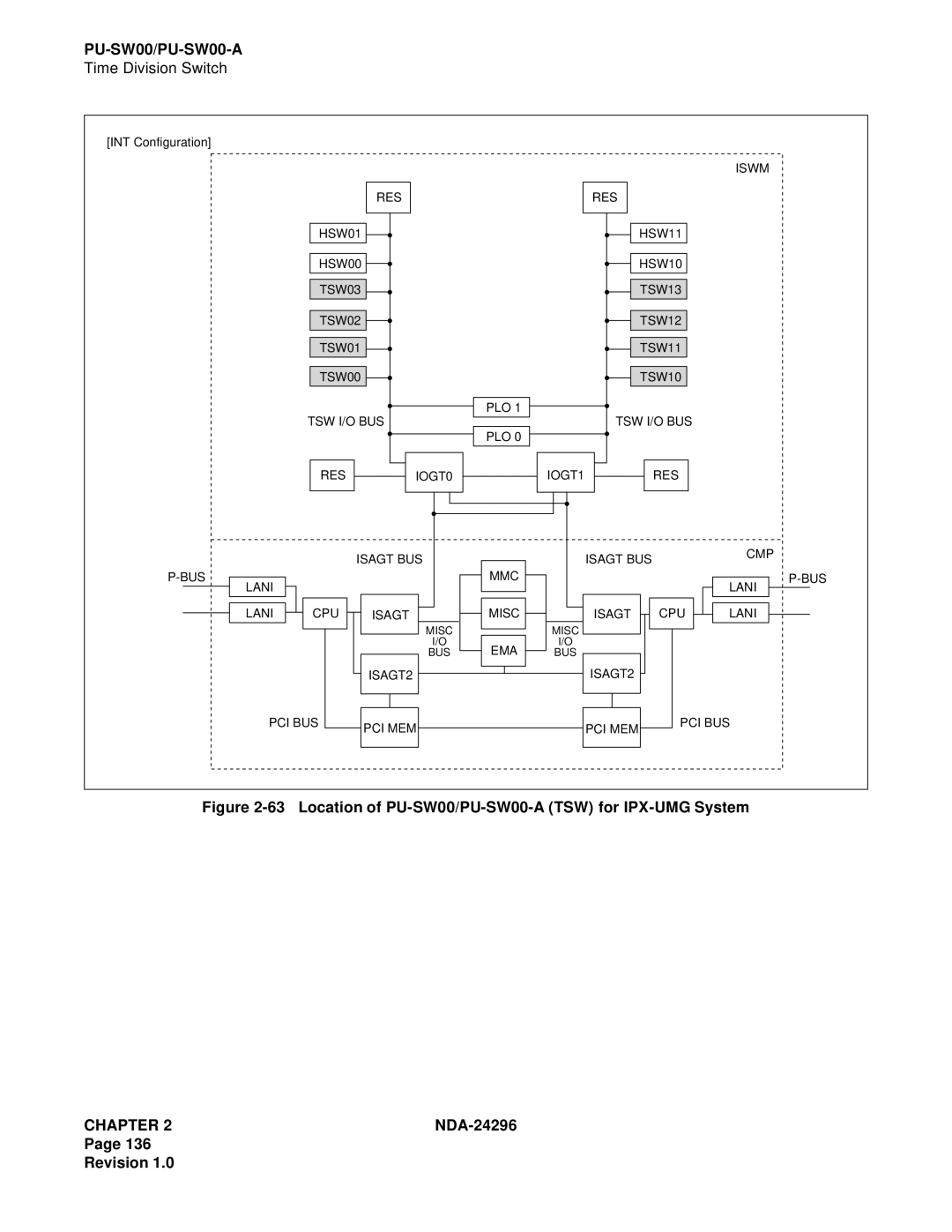

PU-SW00/PU-SW00-A

PU-SW00/PU-SW00-A

63 Location of PU-SW00/PU-SW00-A TSW for IPX-U System

63 Location of PU-SW00/PU-SW00-A TSW for IPX-UMG System

64 Face Layout of PU-SW00/PU-SW00-A TSW

Hckalm

SWE5 OFF

TSW MB

TSW MBR

TSW MB TSW MBR

Highway Switch

PU-SW01

PU-SW01

65 Location of PU-SW01 HSW for IPX-U System

65 Location of PU-SW01 HSW for IPX-UMG System

66 Face Layout of PU-SW01 HSW

Ckale

Pwpalm

Ckalf

Ckald

CKAL1

CKAL3

CKAL2

CKAL0

PZ-GT13

Industrial Standard Architecture Gateway

PZ-GT13

68 Location of PZ-GT13 Isagt in the IPX-U System ISW

70 Face Layout of PZ-GT13 Isagt

PZ-GT16

PZ-GT16

72 External Interface for PZ-GT16

73 Face Layout of PZ-GT16 Isagt

PZ-GT20

Industry Standard Architecture Gateway

PZ-GT20

LPIMG0/4/8/12

NDA-24296

PZ-M565

79 Face Layout of PZ-M565 Isagt Card

PZ-ME44

PCI Memory

PZ-ME44

82 Face Layout of PZ-ME44 PCI MEM Card

Soft

PZ-PC19

Local Area Network Interface

PZ-PC19

84 External Interface for PZ-PC19

EST2

EST0

EST1

EST3

Switch Setting Sheet No switch settings are required

PZ-PC22

PZ-PC22

88 Location of PZ-PC22

Txrx

Link

COL

90 External Interface for PZ-PC22 Lani

PZ-PC23

PZ-PC23

92 Location for PZ-PC23

LINK0/1

TXRX0/1

94 External Interface for PZ-PC23 Lani

LINE/TRUNK Circuit Card Reference

PA-CFTB

Party Conference Trunk

PA-CFTB

Mounting Module

BL0

BL7

Switch Setting Standard Meaning Name

SW2

Module Slot Switch Switch Shape Remarks Name

PIM SW0 SW1

PA-CK14

Oscillator

PA-CK14

Face Layout of PA-CK14 OSC Card

CLKOUT0

CLKOUT1

Phase Lock Oscillator

PH-CK16

PH-CK16

PH-CK16

Music Source NDA-24296

Face Layout of PH-CK16 PLO

Palm

SW03 Fixed to

SW8F

Swab

Tswm

Connecting Route Diagram

Swac SW8F

Swab

PH-CK16-A

PH-CK16-A

11 Location of PH-CK16-A PLO in IPX-U/IPX-UMG System

TSWMIMG1

12 Face Layout of PH-CK16-A PLO

Ckpkg

ALM0

ALM1

When clock source failure has occurred, the PLO keeps on

Mounted in TSWM0 of IPX-U/IPX-UMG System

PH-CK16-A

SW12 Not used

13 PLO Pin Assignments for Receiving Clock 4 IMG System 1/2

13 PLO Pin Assignments for Receiving Clock 4 IMG System 2/2

14 PLO Pin Assignment for Receiving Clock Iswm 1/2

Iswm Baseu ISW/CMG PLO#1 EXCLK1 PLO#0 EXCLK0

LN/LMG

17 LT Connector Lead Location of PLO ISWM-TSWM0/1

IMG

Switch Name Switch Shape

19 Connection of External Music-On-Hold

PH-CK17

PH-CK17

PH-CK17

21 Music Source NDA-24296

22 Face Layout of PH-CK17 PLO

Lamp Name Color State

KHz of Frame Head signals are extracted from the DCS signals

SW06

Don’t care

23 LT Connector Lead Location of PLO Tswm NDA-24296

24 Connecting Route Diagram

SW01 SW02

PH-CK17-A

PH-CK17-A

26 Location of PH-CK17-A PLO in IPX-U/IPX-UMG System

TSWM0IMG1

27 Face Layout of PH-CK17-A PLO

Palm

Switch Setting Standard Meaning Name

This circuit card is used associated with Sync PA-CK16

5 m Frame Pulse FP is supplied by the Sync card

DIU 0 is not used

Not used SW12

28 PLO Pin Assignments for Receiving Clock 4 IMG System 1/2

28 PLO Pin Assignments for Receiving Clock 4 IMG 2/2

29 PLO Pin Assignment for Receiving Clock Iswm 1/2

NDA-24296CHAPTER

LN/LMG

32 LT Connector Lead Location of PLO ISWM-TSWM0/1 NDA-24296

IMG

34 Connection of External Music-On-Hold

SW03 SW10 SW11 SW12

PH-CK18

Clock

PH-CK18

Mounting Module TSWM1IMG2/6/10/14

Lamp Color Meaning

37 LT Connector Lead Location ISWM-TSWM0/1

Switch Setting Sheet

PA-8COTBJ

Central Office Trunk

PA-8COTBJ

39 Face Layout of PA-8COTBJ 8COT

Switch Setting Standard Meaning

40 LT Connector Leads Accommodation

EIA/TIA 464-A

PIM

PA-16COTBE

PA-16COTBE

PIM

43 Face Layout of PA-16 Cotbe 16COT

No Circuit make busy

MB8 ~ No Circuit make busy

Wink Signal Detection Time

Call abandon detecting condition Disconnection if ringing

Artd Apad Transmit Receive Remarks PAD

44 LT Connector Leads Accommodation 1/2

44 LT Connector Leads Accommodation 2/2 NDA-24296

45 Connecting Route Diagram 1/2

Module Slot no Switch Name Switch Shape Remarks

PA-CS02-C

Attendant Interface

PA-CS02-C

47 Face Layout of PA-CS02-C 2ATI

BLA0

BLS0

BLS1

BLA1

SW8 OFF

48 LT Connector Lead Accommodation NDA-24296

Module

PA-CS08

Hotel Attendant Interface

PA-CS08

OFF

Lamp Color State

SW02 TAS0

SW9

51 LT Connector Lead Location PIM NDA-24296

Switch Switch Shape Remarks

PA-CS08-B

PA-CS08-B

PIM

53 Face Layout of PA-CS08-B Hmati

Lamp Color State

Circuit card make busy

OFF SW9

54 LT Connector Lead Accommodation NDA-24296

UP Circuit card make busy

PA-CS33

PA-CS33

56 Face Layout of PA-CS33 ATI

Green Remains lit while circuit card is operating normally

TAS#0

Desk Console Expanded LCD Display available

On Console is shown below

58 Connecting Route Diagram NDA-24296

59 Desk Console Connection

PBX

PBX

No. of DC -48V cablesNo. of GND cables

61 LT Connector Lead Location PIM

SW00 SW01

PA-8LCBR

Line Circuit

PA-8LCBR

PIM

63 Face Layout of PA-8LCBR 8LC

Lamp Name Color Status Meaning

OFF

Switch Setting

BNW2 on BNW1 OFF

64 LT Connector Leads Accommodation

65 Connecting Route Diagram

SW00 SW10 SW01

PA-16LCBE

PA-16LCBE

PIM

67 Face Layout of PA-16LCBE 16LC

BL1S OFF

SW0 OFF

However, when the station line is long PBX

Telephone Set, rearrange the switch setting

Polarity Reversal as Disconnect Signal

Stutter Dial Tone Available

68 LT Connector Leads Accommodation 1/2 NDA-24296

68 LT Connector Leads Accommodation 2/2

69 Connecting Route Diagram

Module Slot NO. Switch Name Switch Shape Remarks

SW0 SW1 PIM

PA-16LCBJ-A

PA-16LCBJ-A

PIM

71 Face Layout of PA-16LCBJ-A 16LC

2Dial pulses are being received. While dial

Circuit no Kind of Balancing Network

BNW8~15 Compromise

72 LT Connector Lead Accommodation 1/2 NDA-24296

72 LT Connector Lead Accommodation 2/2

73 Connecting Route Diagram NDA-24296

Module Slot No

PA-16LCBJ-B

PA-16LCBJ-B

PIM

75 Face Layout of PA-16LCBJ-B 16LC

Lamp Color State Meaning Name

SW00MB Card make-busy Inserted state

Switch Name Setting

OFF

76 LT Connector Leads Accommodation 1/2

76 LT Connector Leads Accommodation 2/2 NDA-24296

77 Connecting Route Diagram

SW00 SW13 SW15

PA-16LCBW

PA-16LCBW

79 Face Layout of PA-16LCBW LC NDA-24296

Lamp Name Lamp Status Meaning of Indication Color

Switch Function Switch Setting Meaning

350 21∝ 600 Compromise ImpedanceEIA/TIA-464B

Switch Function Meaning Setting

Message Waiting Lamp

See also Connecting Route Diagram Figure

80 LT Connector Lead Accommodation 2/2

Connecting Route Diagram for the PA-16 Lcbw LC is as follows

SW00 SW10 BNW0-7 SW11 BNW8-15 SW14 SW15 SW16 SW17

PA-16LCBY

PA-16LCBY

83 Face Layout of PA-16LCBYLC Card

Lamp Name Lamp Status Meaning of Indication

Neax 2400 PAD

OFF ICS-PBX PAD

SW19

For North America, Other Country µ Law

84 LT Connector Lead Accommodation 1/2

84 LT Connector Lead Accommodation 2/2

Connecting Route Diagram for the PA-16 Lcby LC is as follows

Switch Shape Remarks

PA-16ELCJ

PA-16ELCJ

Electric Line Current

Firmware

87 Face Layout of PA-16ELCJ ELC Card NDA-24296

Green Remains lit while on-line operations are normal

SW01-1

ELC/DLC

88 LT Connector Lead Location 16ELC Mode 1/2

16ELC mode

Module

PA-16ELCJ-B

Electronic Line Circuit

PA-16ELCJ-B

90 Face Layout of PA-16ELCJ-B ELC Card

Lamp Name Color State

LP-PM

SW10-3 OFF, SW10-4 OFF SW10-3 OFF, SW10-4 on

91 LT Connector Lead Accommodation 16ELC Mode 1/2

91 LT Connector Lead Accommodation 16ELC Mode 2/2 NDA-24296

8DLC mode

SW10 SW11

PA-FCHA

Fusion Call Control Handler

PA-FCHA

94 Face Layout of PA-FCHA FCH Card

LYR

Load

Turn on the MNT3 switch Flip the MB switch

This SW designates the D/I channel

Set the corresponding SWs to on for D/I, OFF for Denial

Positive logic for the D/I

PA-FCHA

95 FCH/HUB/DTI Connection

96 FCH Cascade Connection NDA-24296

SW12 SW13

PA-24LCBV

PA-24LCBV

LED Name Color LED Status Description

OPE1

OPE2

This switch North America, Other Country A/µ Law

350 600 Compromise ImpedanceEIA/TIA-464A

SW00 SW10

99 LT Connector Lead Location PIM 1/2

99 LT Connector Lead Location PIM 2/2 NDA-24296

LC Connector Leads

101 Connecting Route Diagram

LC Cable Connection

103 Cable Running for LC Cable Example NDA-24296

Power Failure Transfer

PA-M69

PA-M69

105 Face Layout of PA-M69 PFT, 12NCU

Switch Name Setting Standard Meaning

106 LT Connector Leads Accommodation

107 NCU Connector Accommodation

108 Connecting Route Diagram

SW0 PIM Down

PA-M96

110 Face Layout of PA-M96 HUB Card

CRS0~CRS7

ST0~ST7

Polarity indication on the STn lamps for TPn-X ports n = 0~7

FCH/HUB/DTI/LANI Connection

SEL

PA-M103

113 Face layout of PA-M103 HUB Card

Switch Settings No switch settings are required

114 External Interface for PA-M103 HUB Card

PA-8RSTK

Register Sender Trunk

PA-8RSTK

PIM

BLR0

BLR7 OFF

BLS7 OFF

Register make busy of the corresponding circuit

Sender make busy of the corresponding circuit

Meaning Name

OFF SW0

MFR Receive Specification AT&T

MBR0-3 MBR4-7 MBS0-3

PA-8RSTM

PA-8RSTM

118 Face Layout of PA-8RSTM 8RST

Register Make-busy of the corresponding circuit

Sender Make-busy of the corresponding circuit

17 dBm0

MFR Receive Specification ITU-T No

MBR0-3 SW01 MBR4-7 SW03 MBS0-3 SW02

PA-8RSTY

PA-8RSTY

120 Face Layout of PA-8RSTY 8RST NDA-24296

Lamp Name Color State

SW01 Register make busy of the corresponding circuit MBR0-7

Switch Function Switch Setting Meaning

MFR/PBR

SW13 MF Transmission Level-9dBm

SW00 Standard Setting Down SW01 MBR0-7 SW02 MBS0-7 SW10 SW11

SW12 SW13 SW14 SW15 SW16 SW17

PA-SDTA

SDH/SONET Digital Trunk

PA-SDTA

PIM

122 PA-SDTA Card Mounted in the 1 IMG System

123 Face Layout of PA-SDTA SDT

OPT

LPB

SW11 PAD function is effective

PA-SDTA PA-SDTB

125 Example of Cable Connection for 1-IMG System

PIM1

IMG0 IMG1 IMG2 IMG3 PIM3

PIM2

PIM0

Module Time Slots Cable Connections Group From

SDT

SDT PA-SDTB

126 Example of Cable Connection for 4-IMG System

127 Location of MUXxxx Connectors for SDT

128 Level Diagram

Condition Level Margin

129 LT Connector Lead Accommodation

4 5 6 7 3 4 5 6 7

PA-SDTB

130 Location of PA-SDTB SDT Card in the System

00 01 02 03 04 05 06 07 08 09 10 11 12 13 15 16 18 19 21 22

131 Face Layout of PA-SDTB SDT

32MALA

2MALA

2MALB

32MALB

Switch Name Switch Shape Chapter

PA-2CCHA

Common Channel Handler

PA-2CCHA

PIM

DOPE0

DOPE1

SW01 No Circuit make busy request

MODE0

MODE1

SW13 For No Circuit

134 LT Connector Lead Accommodation 1/2

134 LT Connector Lead Accommodation 2/2

135 Connecting Route Diagram Digital Ccis

136 Connecting Route Diagram Analog Ccis

Module Slot no Switch Switch Shape Remarks Name

PA-24CCTA

Common Channel Trunk

PA-24CCTA

PIM

138 Face Layout of PA-24CCTA 24CCT

BER

PCM

FRM

RMT

139 Available Locations for Loopback Testing

SW00/MB

SW02 Transmission Guard Timer Setting sec

SW11/39 PAD Control

SW12/58 PAD Pattern Selection

SW15/25 Impedance Setting 100 Ω

SW18/11B Fixed to all on Selection of CCH Built-in CCH

Digital PAD Setting Table for PA-24CCTA

Artd

140 LT Connector Lead Accommodation

141 Connecting Route Diagram

PIM SW00/MB Down

SW14/5D Multiframe CCT Standard SW15/25 SW17/6G

PA-2DCHA

Channel Handler

PA-2DCHA

PIM

143 Face Layout of PA-2DCHA 2DCH

Switch

SW11 AT & T Bell

Channel Mode Selection Network Side

144 LT Connector Leads Accommodation 1/2 NDA-24296

144 LT Connector Leads Accommodation 2/2

145 Connecting Route Diagram 1/2

145 Connecting Route Diagram 2/2

SW01 SW01-2, 3 Not used SW02 SW10

PA-ILCG

Isdn Terminal Line Circuit

PA-ILCG

Mounting Condition

147 Face Layout of PA-ILCG ILC

LYR4

PWR4

PKT

Not used Fixed to on Channel Packet Service Available

Mode

148 LT Connector Lead Accommodation

149 Connecting Route Diagram NDA-24296

Switch Setting Sheet

PA-4ILCH

Isdn Line Circuit

PA-4ILCH

PIM

151 Face Layout of PA-4ILCH 4ILC

Nope

MBR OFF

LPB OFF

Fixed SW11 Sealing Current is not supplied

Data link mode for Layer 2 of line

152 LT Connector Leads Accommodation

153 Connecting Route Diagram

LPB Mode PIM

PA-8ILCE-A

PA-8ILCE-A

PIM

155 Face Layout of PA-8ILCE-A ILC

Lamp Name Color Description

Circuit #7 Short Passive Connection

OFF

PAD Level Adjustment

Switch Setting Standard Meaning

See also Connecting Route Diagram. Figure

156 LT Connector Lead Accommodation 2/2

Point-to-Point

MODE0 MODE1

PA-4DATA

Digital Announcement Trunk

PA-4DATA

PIM

BL4

BL3

Be mixed assigned

SW5

SW6 OFF

SW7 OFF

Start SW8

Mrcs

Mbrq OFF

160 LT Connector Lead Accommodation NDA-24296

Switch Setting Description

SW6

NDA-24296CHAPTER

SW1 SW2 SW3 SW4 SW5

SW6 PIM SW7 Start

Mbreq

PA-4DATB

PA-4DATB

PIM

162 Face Layout of PA-4DATB DAT

Mbrq

Recording/Playback Timer should

Switch Setting Description Shape

JP0 Left

Right

163 LT Connector Lead Accommodation NDA-24296

HOW to Record a Message

JP0

HOW to Play Back the Recorded Message

Module Slot no Switch Name Switch Shape

Start Mbrq Mrcs SW1 SW2 SW3 SW4 SW5 SW6

SW7 JP0

TEL PIM Lpra

LPM

165 Face Layout of PH-M16 Ltst Card

SW0

Lamp Color Description Name

Misc Connector Accommodation

167 Connecting Route Diagram

Onmb OFF

PA-4AMPC

AMP Pool Trunk

PA-4AMPC

PIM

169 Face Layout of PA-4AMPC 4AMP

BL3 OFF

SW00

When this card works as AGC

SW03 SW04

PA-8TLTR

Tie Line Trunk

PA-8TLTR

PIM

171 Face Layout of PA-8TLTR TLT Card

BL7 OFF

MB0 Make busy of the No circuit SW01

SW1 OFF

Programmable PAD P1 Value 0 dB

Programmable PAD P2 Value 0.5 dB SW25 P2 Values is total

SW40

~ 4

LD/2W E&M

Artd Command

Apad Command

Send Receive

172 LT Connector Lead Accommodation 1/2

172 LT Connector Lead Accommodation 2/2

LD/DID

4W E&M

ODT Cable

ODT CABLE-A

MB0-7 SW01

PA-M87

Recording / Paging Device Adapter

PIM

178 Face Layout of PA-M87 RECC/PGADP

ATT0 ~ ATT5

Recording/Paging start control at Attcon #0 by loop

VR0

VR1

179 REC/PGA Connector Leads

180 Connecting Route Diagram 1/4

180 Connecting Route Diagram 2/4

180 Connecting Route Diagram 3/4

180 Connecting Route Diagram 4/4

SW10

PA-24PRTB-A

Primary Rate Interface Trunk

PA-24PRTB-A

182 Face Layout of PA-24PRTB-A 24PRT NDA-24296

PER

Dope

RKT

AT&T #4/#5 ESS

SW3 OFF

Setting Table

Digital PAD Setting Table for PA-24PRTB-A

183 LT Connector Lead Accommodation

184 Connecting Route Diagram

PIM Mode SW0 SW1 SW2

SW5 Down

PA-24DTR DTI

Digital Trunk Interface

PA-24DTR DTI

PIM

186 Face Layout of PA-24DTR DTI

Red Lights in the case of input signal down PCM Loss

187 Available Locations for Loopback Testing

Transformer at Middle Point Transmission Open

SW10/4D Transmission Signal a Logic Negative

Zero Code Suppression is provided

SW13/6C

Digital PAD Setting Table for PA-24DTR DTI

188 LT Connector Lead Accommodation

189 Connecting Route Diagram

SW00/MB Down

PA-24DTR DLI

Digital Line Interface

PA-24DTR DLI

PIM

191 Face Layout of PA-24DTR DLI

Lamp Name Color State

192 Available Locations for Loopback Testing

Not to be sent out One Digit Dialing Valid

RMT Alarm Sending To be sent out

When setting this key, refer to Digital PAD Setting

SW13/6C Main Signal All 1 Supervision Valid

Digital PAD Setting Table for PA-24DTR DLI

193 LT Connector Lead Accommodation

194 Connecting Route Diagram

Equalizer Setting

This page is for your notes