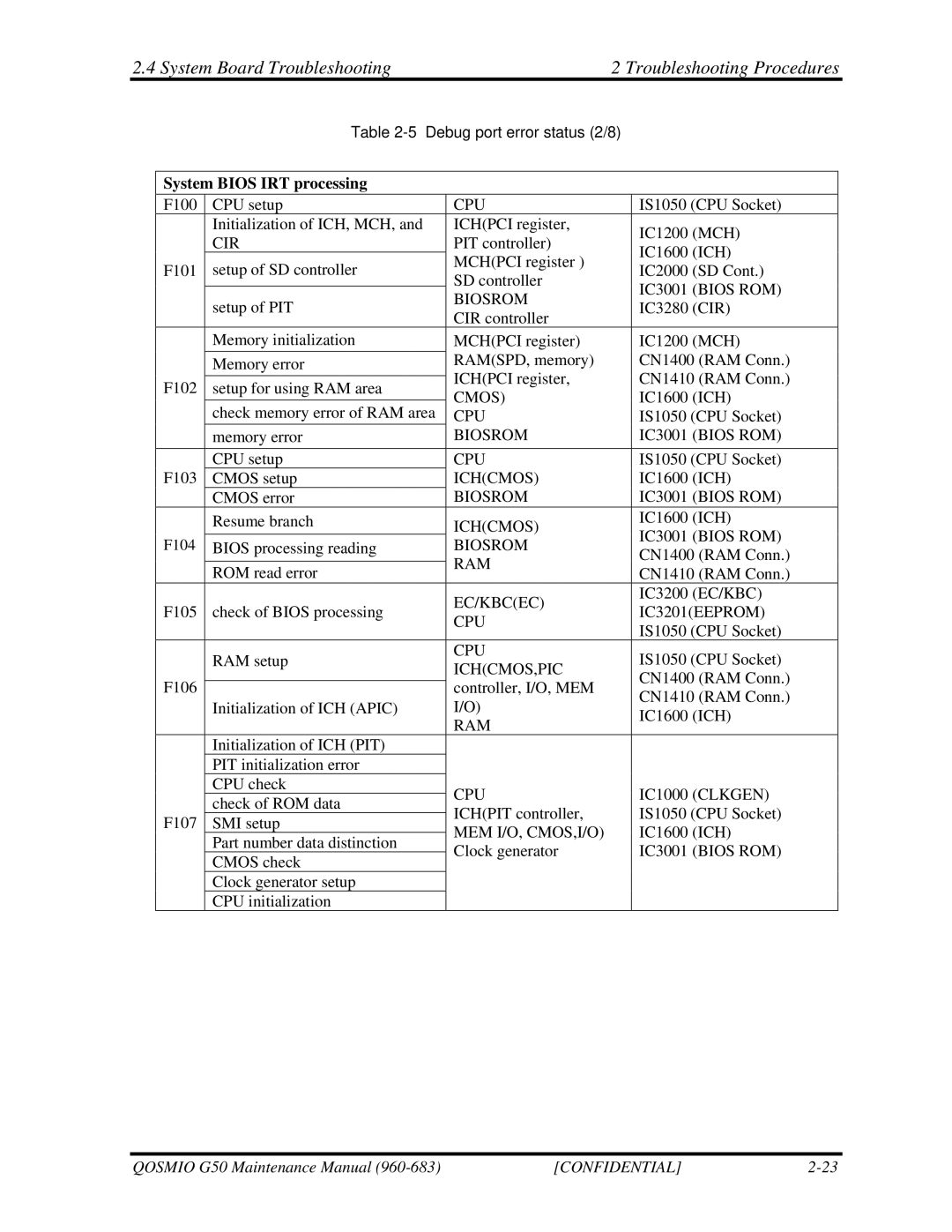

2.4 System Board Troubleshooting | 2 Troubleshooting Procedures |

Table

System BIOS IRT processing

F100 | CPU setup | CPU | IS1050 (CPU Socket) | |

| Initialization of ICH, MCH, and | ICH(PCI register, | IC1200 (MCH) | |

| CIR | PIT controller) | ||

| IC1600 (ICH) | |||

F101 | setup of SD controller | MCH(PCI register ) | ||

IC2000 (SD Cont.) | ||||

SD controller | ||||

|

| IC3001 (BIOS ROM) | ||

| setup of PIT | BIOSROM | ||

| IC3280 (CIR) | |||

| CIR controller | |||

|

|

| ||

| Memory initialization | MCH(PCI register) | IC1200 (MCH) | |

| Memory error | RAM(SPD, memory) | CN1400 (RAM Conn.) | |

F102 |

| ICH(PCI register, | CN1410 (RAM Conn.) | |

setup for using RAM area | ||||

CMOS) | IC1600 (ICH) | |||

| check memory error of RAM area | |||

| CPU | IS1050 (CPU Socket) | ||

| memory error | BIOSROM | IC3001 (BIOS ROM) | |

| CPU setup | CPU | IS1050 (CPU Socket) | |

F103 | CMOS setup | ICH(CMOS) | IC1600 (ICH) | |

| CMOS error | BIOSROM | IC3001 (BIOS ROM) | |

| Resume branch | ICH(CMOS) | IC1600 (ICH) | |

F104 |

| BIOSROM | IC3001 (BIOS ROM) | |

BIOS processing reading | ||||

CN1400 (RAM Conn.) | ||||

|

| RAM | ||

| ROM read error | CN1410 (RAM Conn.) | ||

|

| |||

F105 | check of BIOS processing | EC/KBC(EC) | IC3200 (EC/KBC) | |

IC3201(EEPROM) | ||||

CPU | ||||

|

| IS1050 (CPU Socket) | ||

|

|

| ||

| RAM setup | CPU | IS1050 (CPU Socket) | |

| ICH(CMOS,PIC | |||

F106 |

| CN1400 (RAM Conn.) | ||

| controller, I/O, MEM | |||

| ||||

| CN1410 (RAM Conn.) | |||

| Initialization of ICH (APIC) | I/O) | ||

| IC1600 (ICH) | |||

|

| RAM | ||

|

|

| ||

| Initialization of ICH (PIT) |

|

| |

| PIT initialization error |

|

| |

| CPU check | CPU | IC1000 (CLKGEN) | |

| check of ROM data | |||

F107 | ICH(PIT controller, | IS1050 (CPU Socket) | ||

SMI setup | ||||

MEM I/O, CMOS,I/O) | IC1600 (ICH) | |||

| Part number data distinction | |||

| Clock generator | IC3001 (BIOS ROM) | ||

| CMOS check | |||

|

|

| ||

| Clock generator setup |

|

| |

| CPU initialization |

|

|

QOSMIO G50 Maintenance Manual | [CONFIDENTIAL] |