ASIC Driver Commands on Cisco IOS XR Software

show controllers plim asic

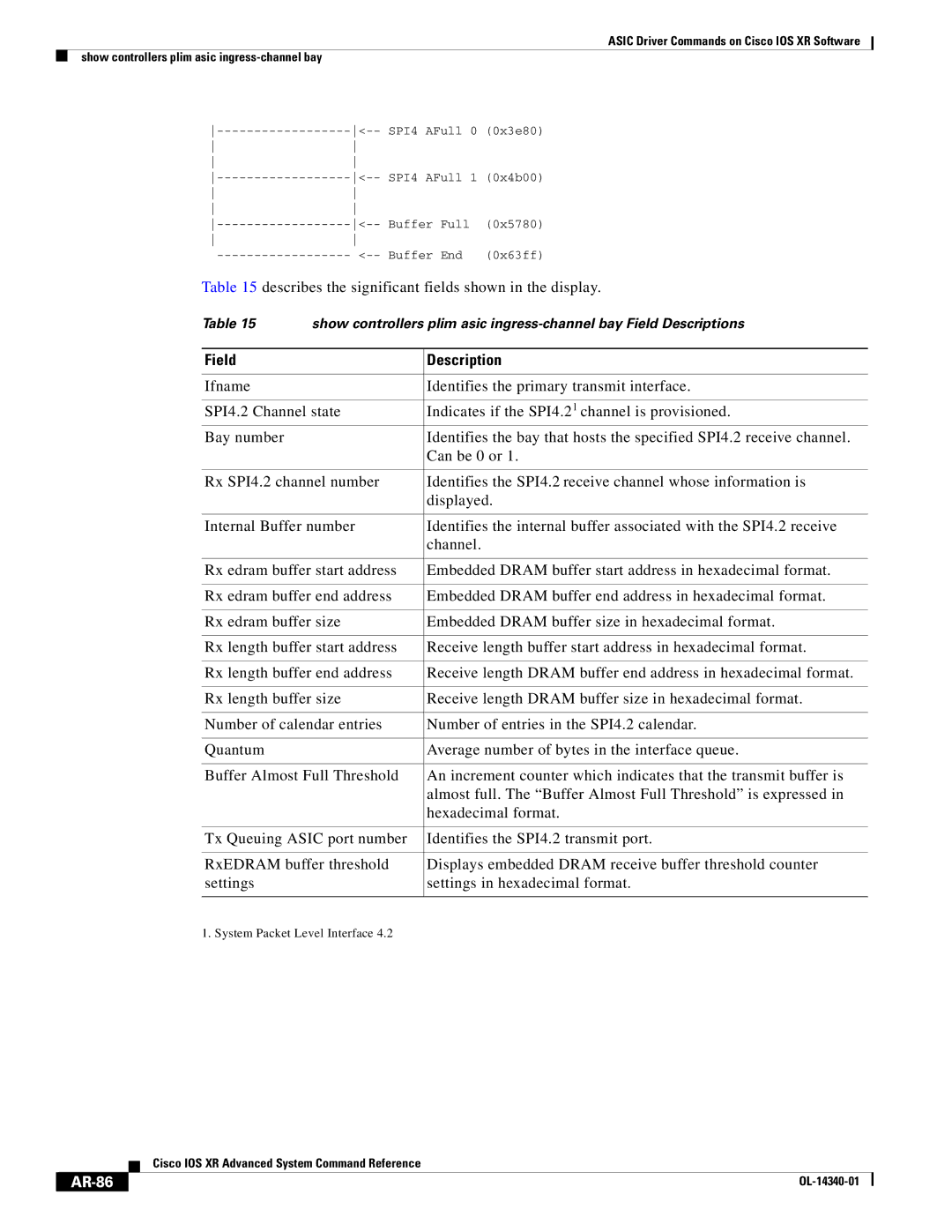

SPI4 AFull 0 | (0x3e80) | ||

|

| ||

|

| ||

SPI4 AFull 1 | (0x4b00) | ||

|

| ||

|

| ||

Buffer Full | (0x5780) | ||

|

| ||

Buffer End | (0x63ff) |

Table 15 describes the significant fields shown in the display.

Table 15 | show controllers plim asic | |

|

|

|

Field |

| Description |

|

|

|

Ifname |

| Identifies the primary transmit interface. |

|

| |

SPI4.2 Channel state | Indicates if the SPI4.21 channel is provisioned. | |

Bay number |

| Identifies the bay that hosts the specified SPI4.2 receive channel. |

|

| Can be 0 or 1. |

|

| |

Rx SPI4.2 channel number | Identifies the SPI4.2 receive channel whose information is | |

|

| displayed. |

|

| |

Internal Buffer number | Identifies the internal buffer associated with the SPI4.2 receive | |

|

| channel. |

|

| |

Rx edram buffer start address | Embedded DRAM buffer start address in hexadecimal format. | |

|

| |

Rx edram buffer end address | Embedded DRAM buffer end address in hexadecimal format. | |

|

| |

Rx edram buffer size | Embedded DRAM buffer size in hexadecimal format. | |

|

| |

Rx length buffer start address | Receive length buffer start address in hexadecimal format. | |

|

| |

Rx length buffer end address | Receive length DRAM buffer end address in hexadecimal format. | |

|

| |

Rx length buffer size | Receive length DRAM buffer size in hexadecimal format. | |

|

| |

Number of calendar entries | Number of entries in the SPI4.2 calendar. | |

|

|

|

Quantum |

| Average number of bytes in the interface queue. |

|

| |

Buffer Almost Full Threshold | An increment counter which indicates that the transmit buffer is | |

|

| almost full. The “Buffer Almost Full Threshold” is expressed in |

|

| hexadecimal format. |

|

| |

Tx Queuing ASIC port number | Identifies the SPI4.2 transmit port. | |

|

| |

RxEDRAM buffer threshold | Displays embedded DRAM receive buffer threshold counter | |

settings |

| settings in hexadecimal format. |

|

|

|

1. System Packet Level Interface 4.2

| Cisco IOS XR Advanced System Command Reference |

|